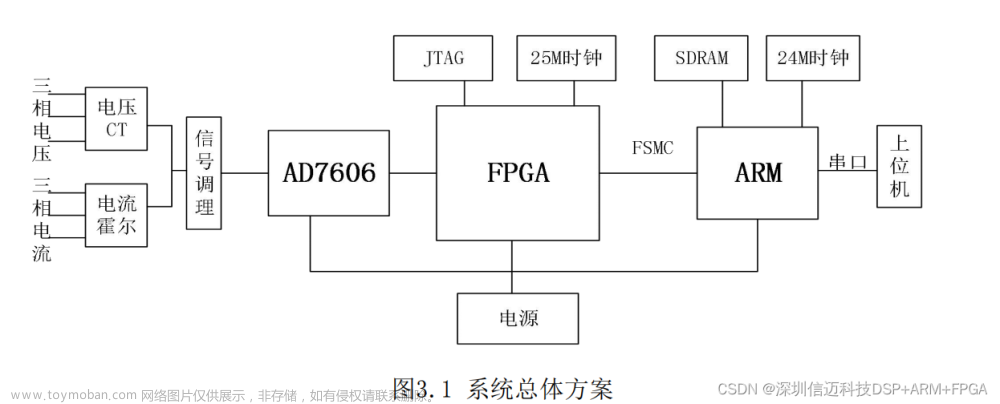

路通用

I/O

信号等,在运动控制部分,运动控制实验平台主要控制的是输出 12

路差分信号、

6

路驱动器使能信号以及

24

路通用输出信号等

[49-50]

。在整个运动

控制的组成部分中,可以将其分为

DSP

数据处理模块,

FPGA

模块以及供电模

块,整个硬件部分的电路结构如图

2-1

所示。

2.2 DSP

数据处理模块的研究与设计(

Research and design of DSP

data processing module

)

2.2.1 TMS320C6713 DSP

处理器的特点

TI

公司设计的

C6000

系列的

DSP

的优点主要如下

[51]

:

(

1

)在哈弗结构的基础上实现数据与程序部分的分开存储,在数据总线部

分使用的是独立的模式;

(2)在指令部分,可以实现并行处理的过程,而且能够在不同的功能单元

内对数据进行取值、译码、取操作;

(3)在使用辅助寄存器的基础上采用多总线的方式实现自主的增加地址操

作,并且能够并发实现对数据空间进行很多次的访问;

(4)为了提高片内的工作频率采用的方式是数字锁相电路;

(5)内部配有专用的累加器用于硬件乘法模式;

(6)为了保证系统的稳定性要求,采用的是超长的指令字模式,在

8

个并

行处理单元的基础上拥有

256

位的总字长,再这样的条件下能够实现的是

2400M/PS

;

(7)采用二级缓冲处理,其中包括一级程序和数据缓冲部分,该缓冲部分

的大小都是

4KByte

,并且还拥有

256Kbyte

的二级额外匹配内存

[52]

(8)为了实现与 SDRAM、Flash ROM 以及异步存储器能够进行快速的通讯功能,使用的是 EDMA 丰富外设总线模式. TMS320C6713 结构如图 2-2 所示。

文章来源:https://www.toymoban.com/news/detail-737137.html

2.2.2 TMS320C6713 DSP

数据处理模块的结构分析

在

C60000

系列中,比较典型的

DSP

芯片型号为

TMS320C6713

,本文选用

此型号此构成了实验平台。

DSP

功能模块主要实现的功能主要为多轴运动数据

信息采集、存储以及传输、自动与手动恢复等。在数据处理模块中还需要其他设

备才能完成相应的功能,其中就包括:供电模块、时钟模块、复位模块、

JTAG

模

块、外扩

Flash ROM

和外扩

SDRAM

模块

[53]

。其结构图如图

2-3

所示

:

(

1

)电源模块

为了满足

TMS320C6713

的工作需求,需要配备相应的供电模块,在

TMS320C6713

中使用的是

2

级供电的模式,其中内部的供电使用的是

1.26V

的

电压,在外部使用的是

3.3V

的电压,因此在本电源模块中就需要使用从外部引

入

5V

直流电压的模式,并且通过特定的芯片将其转换成需要的电压,电路设计

图如图

2-4

和

2-5

所示。

(5)伺服控制模块的实现

伺服控制模块主要完成的工作如下

:

①在输入输出开关量接口的部分,该接口包括

HOME

、

LIMIT

和

ALM

部

分,这些部分的信号能够对

SVON

输出信号进行相应的处理工作。对于伺服信

号的功能就是为了控制机器人的电机部分,

HOME

信号的目的是为了能够让电

机在运动过程中根据实际的需求进行回零操作,限位信号的目的就是在电机运动

过程中个,不至于超出事先设定好的位置,报警信号就是当电机发生意外的时候

能够让电机及时停止工作的目的。

②在

PWM

脉冲输出控制电路部分,为了获得相应的

CW

和

CCW

信号,可

以通过

FPGA

的分频产生相应的频率,当进行两项的脉冲信号控制时,

CW 信号

就表示正向转动,

CCW

则表示反向转动,在

FPGA

中输出的信号是需要进行电

平的转换操作,然后进行光耦隔离的操作,最后需要做的是差分处理,通过对信

号进行处理后再将其输入到伺服系统中。

③在反馈脉冲处理电路中,首先需要依靠编码器的反馈信号来判断各个电机

的状态,编码器的信号需要进行差分运算才能转换为单路的信号,然后通过光耦

隔离的操作,最后进行电平转换将信号重新反馈给

FPGA

进行处理,单轴的伺服

控制结构如图

2-14

所示

:

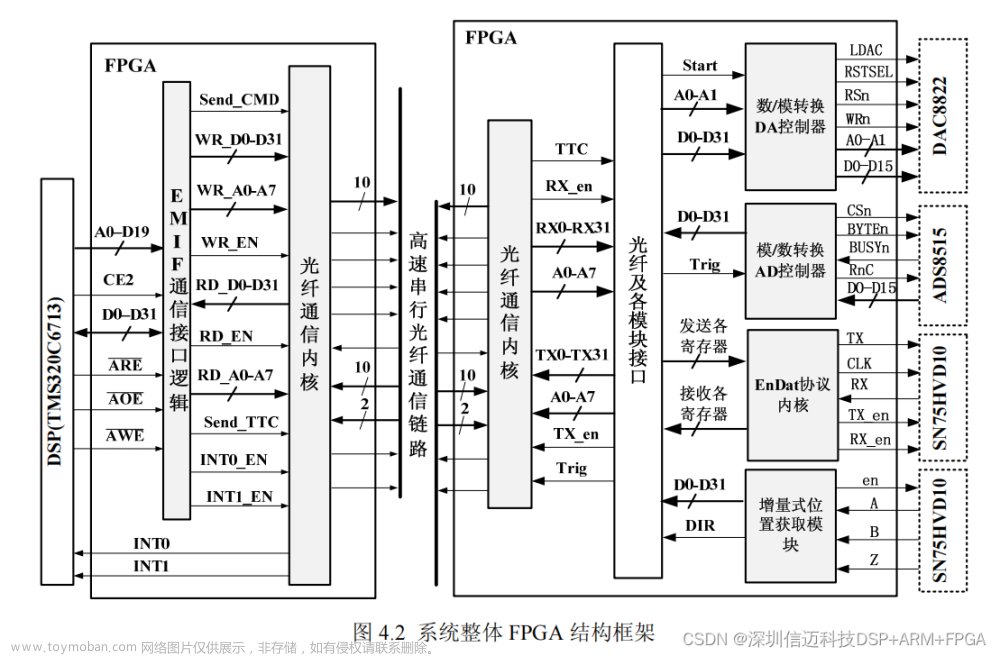

2.4 DSP

与

FPGA

通讯方式设计(

Research and design of FPGA

peripheral circuit module

)

为了进一步充分利用

FPGA

,通过在

DSP

芯片内部的

EMIF

端口来与

FPGA

进行连接,其中,

FPGA

和

TMS320C6713

连接方式如图

2-15

所示。

如图

2-15

所示。以

DSP

为核心处理器,其数据总线用

DO-D15

来表示,地

址总线用

A2-A17

来表示,其中用来控制

FPGA

的操作的是 TSDRAS, TSDCAS

和

TSDWE

作为控制总线,提供给

FPGA

时钟信号的是

ECLKOUT

,组合编码是

通过

TCE2

和

DSP

中的

A2-A17

进行的,如果地址为

OxA000 0000

时,则会生

成一个片选的信号,该片选信号的目的是用来选择

FPGA

中的模块。在

FPGA

与

DSP

进行数据通信的时候,中断信号使得

NT4

由低电平变成了高电平,

DSP

接

收

FPGA

的方式是通过数据总线的方式。

2.5 本章小结(

Summary

)

本章的内容主要是介绍多轴运动控制实验平台的硬件部分,然后对硬件部分

的各个模块进行划分工作,其中包括

DSP

模块、

FPGA

模块和电源模块,然后介

绍了各个模块的设计过程与方案,本文在硬件部分的特点就是使用的

FPGA

来

代替分立元件部分,通过这种方式来进行数据逻辑的连接工作和运动控制,提高

平台的开放性用以不同算法的实验,同时提升多轴运动控制的性能。

信迈提供基于DSP+FPGA多轴运动控制器解闷方案。文章来源地址https://www.toymoban.com/news/detail-737137.html