前言

Vivado是Xilinx公司所开发的一种可编程逻辑器件(FPGA)的设计工具,能够支持开发者进行硬件加速的操作。Vivado的设计理念是使用流程优化,打造具备扩展性的环境来完善硬件设计的各个环节。

其主要特点如下:

——支持多种编程语言:Vivado支持多种编程语言,包括Verilog、VHDL和SystemVerilog,这使得开发人员可以选择最适合自己的编程语言来实现不同的硬件设计需求。

——高效的综合和仿真工具:Vivado提供了高效的综合和仿真工具,可让用户在设计过程中快速捕获和解决问题,从而获得更高的设计效率。

——支持IP及开源工具:为了加快设计的进程,Vivado提供了IP(Intellectual Property,知识产权)库,覆盖了大量复杂系统的核心部分,用户可以利用它们构建更高层次的设计;同时,Vivado也支持开源工具,例如Vivado HLS(High-Level Synthesis)旨在简化使用高级编程语言进行FPGA设计的流程。

——支持并行化设计:Vivado的高度并行化设计流程,使得开发人员能够节省大量时间和精力,从而提高设计效率和生产力。

——强大的开发板支持:Vivado为Xilinx公司的多款FPGA开发板提供了强大的支持,包括Zynq-7000 All Programmable SoC、Kintex UltraScale+ FPGA和Virtex UltraScale+ FPGA等,用户能够利用开发板的灵活性和丰富的资源来完成自己的硬件设计。注:文末附有下载链接!

一、Vivado在Windows系统上的安装

1、将安装包压缩文件进行解压,如下图所示。由于该安装包包含Windows系统安装程序和Linux系统安装程序,故压缩文件较大,解压时间较长,请耐心等待。

2、解压完成后,运行安装包下的Windows系统安装程序,如下图所示。

3、继续下一步安装,如下图所示。

4、选择安装工具,由于安装完全体“Vitis”所占用空间较大,本次选择了“Vivado”进行安装,“Vitis”完全体安装可以参考下一部分的Linux系统上的安装。继续下一步安装,如下图所示。

5、选择安装版本,继续下一步安装,如下图所示。

6、选择全部安装组件,也可根据自己需求进行选择,继续下一步安装,如下图所示。

7、同意许可协议,继续下一步安装,如下图所示。

8、设置安装路径,继续下一步安装,如下图所示。

9、确认无误后开始安装,如下图所示。

10、耐心等待安装,如下图所示。

11、安装过程中需要安装一些驱动组件,进行安装,如下图所示。

12、在等待安装过程中,将Crack文件夹的license文件复制到安装目录的新建license文件夹下,如下图所示。

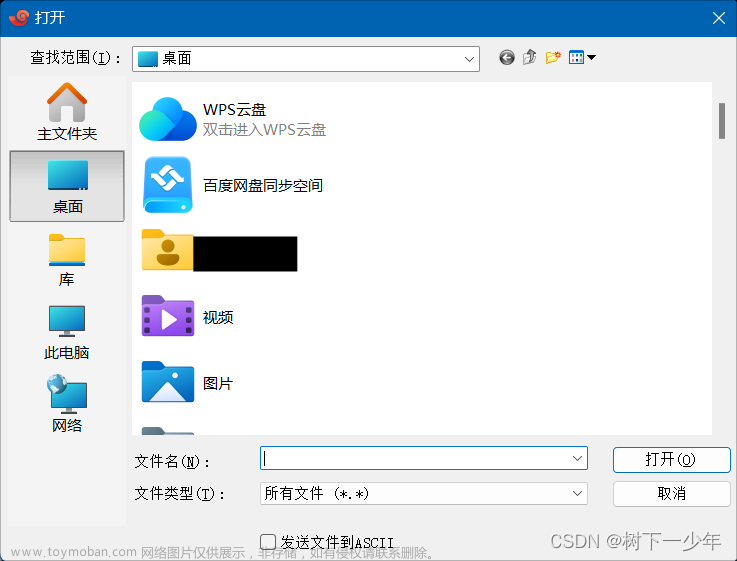

13、在安装过程中跳出许可配置时,选择载入许可文件,选择上一步转存的license文件,如下图所示。

14、载入成功,如下图所示。

15、查看载入的许可信息,如下图所示。

16、安装额外组件,继续下一步安装,如下图所示。

17、同意许可协议,继续下一步安装,如下图所示。

18、进行安装,如下图所示。

19、安装完成,如下图所示。

20、等待直至整个安装完成,如下图所示。

21、启动工具,正常运行,如下图所示。

二、Vivado在Linux系统上的安装

1、将压缩包拷贝到Linux系统下解压(建议),然后在安装文件夹中运行Linux系统的安装程序,如下图所示。(如果运行失败请给xsetup安装程序添加可执行权限!)

2、继续下一步安装,如下图所示。

3、选择安装工具,选择安装安装完全体“Vitis”,继续下一步安装,如下图所示。

4、选择全部安装组件,也可根据自己需求进行选择,继续下一步安装,如下图所示。

5、选择接受许可协议,继续下一步安装,如下图所示。

6、设置安装路径,继续下一步安装,如下图所示。

7、确认无误后开始安装,如下图所示。

8、耐心等待安装,如下图所示。

9、安装完成,如下图所示。

10、根据上一步的提示,我们进入安装目录的脚本文件夹路径下运行安装库程序,如下图所示。

11、脚本运行完成,如下图所示。

12、设置环境变量,编辑用户根目录下的.bashrc文件(cshrc环境的自行转换),将以下内容添加至文件中,保存退出后source .bashrc,使环境变量生效。(其中$Install_DIR/Xilinx替换为自己实际环境的安装目录,export后为空格)

export XILINX_HOME=$Install_DIR/Xilinx

export VIVADO_HOME=$XILINX_HOME/Vivado_2022.2/Vivado/2022.2

export VITIS_HOME=$XILINX_HOME/Vivado_2022.2/Vitis/2022.2

export VITIS_HLS_HOME=$XILINX_HOME/Vivado_2022.2/Vitis_HLS/2022.2

export MODEL_COMPOSER_HOME=$XILINX_HOME/Vivado_2022.2/Model_Composer/2022.2

export XIC_HOME=$XILINX_HOME/Vivado_2022.2/xic

export PATH=$VIVADO_HOME/bin:$VITIS_HOME/bin:$VITIS_HLS_HOME:$MODEL_COMPOSER_HOME/bin:$XIC_HOME/bin:$PATH

13、配置完成环境变量后,在命令框中输入“vivado”回车启动工具,然后选择许可管理进行许可配置,如下图所示。

14、同样是将Crack文件夹的许可文件复制到合适位置后,在许可管理界面选择载入许可文件,然后选择转存的许可文件,如下图所示。(下图所示的许可文件为区分Windows安装与Linux安装,将原Crack文件夹的许可文件进行了重命名,实际内容是一致的)

15、载入成功,如下图所示。

16、查看许可信息,如下图所示。

17、启动工具,正常使用,如下图所示。

文章来源:https://www.toymoban.com/news/detail-737620.html

文章来源:https://www.toymoban.com/news/detail-737620.html

总结

声明:本文第二部分的配置过程只供学习参考,如有商业用途打算,请务必购买和使用正版软件!侵权立删!

本文所用软件获取点击此处。文章来源地址https://www.toymoban.com/news/detail-737620.html

到了这里,关于Xilinx的Vivado 2022.2版本在Windows和Linux系统上的下载配置教程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!