为什么要设置上下拉电阻

这里以高云FPGA的GW1N-UV2QN48C6/I5来举例,这个芯片的上电默认初始化阶段,引脚是弱上来模式,且模式固定不能通过软件的配置来改变。如下图所示:

上图只是为了说明IO口的工作原理,其真实的IO口硬件架构需要去官网看对应的说明文件,通过上图我们可以知道在FPGA初始化阶段,三极管是默认不导通的,此时VCC通过R1连接Vout,Vout相当于初始化阶段就输出一个幅值为VCC的高电平;如果你的负载是高电平导通,则一上电负载就会导通,这个状态一般是我们不想要的,有的FPGA的上拉下拉可以通软件配置来解决,但是有的架构精简的FPGA则只有单纯的上拉模式且不能通过软件更改上下拉配置,如GW1N-UV2QN48C6/I5。对于自带上拉且不能通过软件配置解决的FPGA,我们可以通过直接在IO口上挂下拉电阻来解决。

一、如何设置下拉电阻

挂一个下拉电阻就能让弱上拉变成弱下拉,但是对所挂电阻的阻值确有要求,如下图:

如上图在输出上面挂了一个R2电阻。在没有挂R2之前,从输出端往输入端看进去,输出端有一个等效电阻R(电路上面的戴维南定理类似)因为三极管是断开的,所以初始化阶段等效电阻R相当于无限大(即开路),所以VCC直接通过R1连接到Vout上输出。

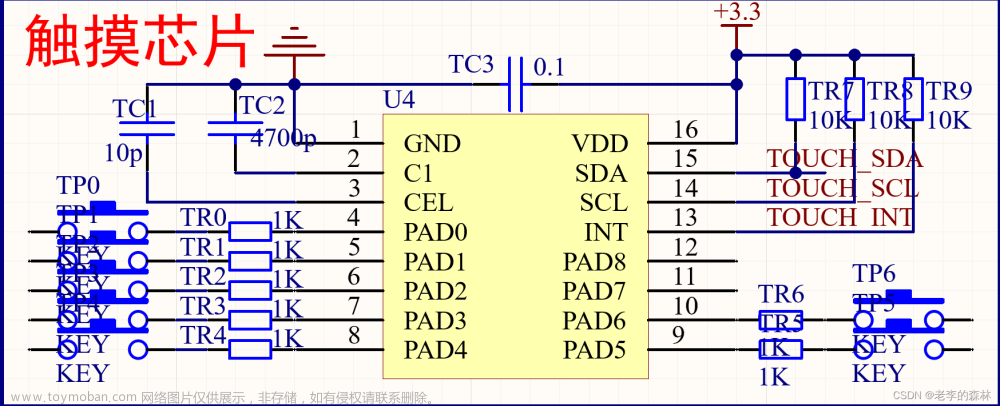

当挂上R2后,R2的值与一个无限大电阻的等效电阻R相比,R2是很小的,此时再从输出端往输入端看,R2与等效电阻R是并联的。一个很小的电阻与一个很大的电阻并联后的值是无限接近于小电阻的值,因此并联后从输出端看向输入端,等效电阻近似的等于R2。所以在FPGA初始化阶段R1与R2处于分压状态,此时Vout=(R2/(R1+R2))*VCC;只要调整R2的值让Vout足够的小那就默认初始化阶段Vout为低电平0。当然,R2也不能去太小,太小初始化过程R1与R2上的电流会过大,功耗会比较大,GW1N-UV2QN48C6/I5的VCC为3.3V,所以R2取1K,这样初始化阶段流过R1与R2的最大电流也就几毫安。文章来源:https://www.toymoban.com/news/detail-737812.html

二、如何设置上拉电阻

如下图,上拉电阻的设置与下拉电阻的设置正好是反过来的,就是通过对R1并联电阻R3让上拉阻抗特别的小,这样在初始化阶段上拉阻抗与R2的分压就会全部落在R2上面,虽然这个值肯定是小于VCC的,但是一个比较大的电压幅值也就默认是一个高电平。这样就是把下拉转化成上拉,当然R3的取值也要合理。 文章来源地址https://www.toymoban.com/news/detail-737812.html

文章来源地址https://www.toymoban.com/news/detail-737812.html

到了这里,关于FPGA芯片IO口上下拉电阻的使用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!