参考Verilog语法 | 教程 (ustc.edu.cn)

1.0 介绍

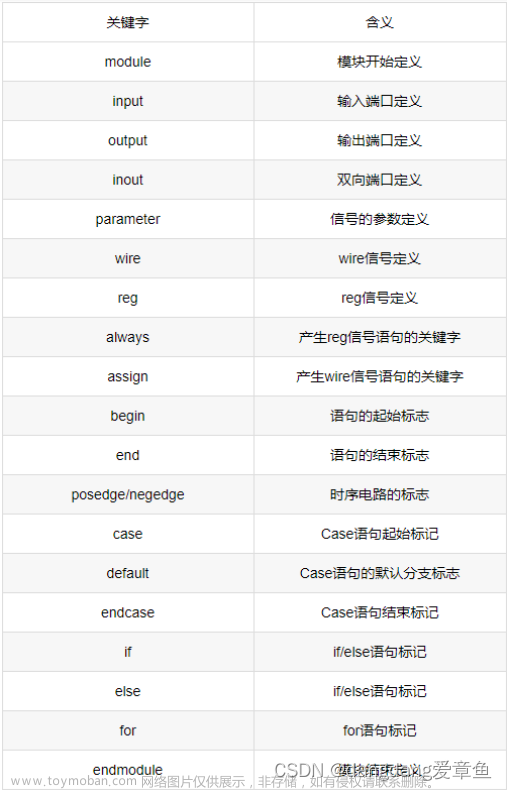

Verilog HDL是一种硬件描述语言(Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

Verilog可以从五个层次对电路(系统)进行描述,包括:系统级、算法级、寄存器传输级(即RTL级)、门级、开关级。我们平时用的最多的为RTL级,故Verilog代码也经常被称为RTL代码。

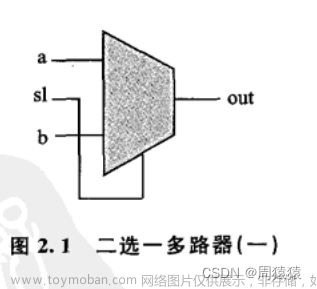

1.1 简单组合逻辑电路

逻辑表达式:

文章来源:https://www.toymoban.com/news/detail-738211.html

文章来源地址https://www.toymoban.com/news/detail-738211.html

module example(

input a,

input b,

input c,

output y1,

output y2);

assign y1 &到了这里,关于【系统设计】Verilog语法及示例(1)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!