一个22年毕业的飞行器控制专业转电子的硬件小白,这篇文章将记录我实习以及工作经历,也就是自己的学习笔记啦。硬件本来就是一个需要积累的东西,学海无涯,希望自己能不断丰富自己。而我的工作岗位是助理工程师,主要是学习绘制原理图,板上测试,FPGA代码的调试等。

2022.5.23

1.用钳子剪线的胶皮的时候,注意别剪断,流出的线不能太长;

2.使用电流源的时候,如果需要50V的电流输入,而只有最大限额的30V,可以通过将两个通道的电流源串联,此时的最大限额为60V,并将一个设置为20V,一个30V;

3.使用万用表的时候,可以用电阻通道,并切换到蜂鸣器模式,若检测时蜂鸣器响,则是导通状态,可以用来检测两个地线是否同时共地;

4.为了防止电流扰动对板子的影响,通常会设置一个隔离电压,例如隔离3.3V,此时通过其他地与其测试,将不会看到电压变化;

5.调试DTECH时,T/R+接RDX+,T/R-接RXD-,其中为短接,为了实现自发自收的功能验证。再通过串口调试工具XCOM21,若能自发自收,则功能正常,调试成功;

6.示波器的使用,可以先进行自检,来调整波形;

7.根据通信协议,来测试通信模块的功能,其中D21 00为头帧,读到则开始计数,80 00,为1000 0000 0000 0000 其中D15为1,则根据通信手册能观测到其功能是否正常,电脑查看则是通过串口,遥控功能查看;

2022.5.24

1.板子有额外的电压供电时,电脑调试的时候需要将ST-link上的电压线取掉,防止两个电压相互抵消,影响功能;

2.测试的时候,上电以后电容会储存电荷,所以进行下一次操作的时候,需要给电容进行放电,可以用电阻负载进行放电。

2022.5.25

1.用keil进行编译时,可能因为内存不足而debug失败,需要我们为其扩大内存,0800-08000;

2.FPGA上的一些引脚需要到官方进行下载,故有的手册上没有引脚定义;

3.电容可以滤波,当检测的时候,噪声很大,可以考虑接入电容。

2022.5.26

1.FPGA通常是分模块,芯片的原理图不用画完,根据使用来画;

2.drc检查很重要,注意分页符,双端网络等;

3.注意书写端口配置的文字;

2022.5.27

1.用万用表检查芯片是否故障,检查是否与地短路,若不该短路的与地短路,则该模块故障。

2.要注意对比原理图,是否有些电阻无故消失,则要后期焊接上。

2022.6.1

1.检查原理图的时候,需要将各个芯片的芯片手册,以及用户使用手册打开进行检查,检查内容包括:3.3V的电压是否能够达到上拉高电平的作用;根据参考电路,检查是否有的地方缺少或者多了电阻电容等值;确定使能作用,比如dr控制各项输入输出;检查时若有一些电阻阻值并不清楚,可以加焊盘,后期再选用特定阻值焊接上。

2.通过Vivado进行简单程序的编码,并查看时序波形图;要理解各行代码的含义。时钟设计中#50表示延迟50个延迟因子(1ns),则周期为100ns,频率为10MHz。

2022.6.2

1.完成了分频的仿真,以及流水灯的仿真,注意代码的规范性,例程也会有错误,需要自己根据情况修改;

2.DCM也就是时钟管理模块;

2022.6.6

1.cadence导出Bom清单的时候需要在Header中添加封装信息 tPCB Footprint,在Combined property string中添加封装描述信息t{PCB Footprint}

2.对导出的Bom清单需要做整理,格式参考苟哥给的模板,其中类型相同的需要合并居中,带星号的为不焊接的部分,放在表的下方。

2022.6.7

- DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。

- zynq ps端介绍 我们使用的普通fpga和arm的结合构成了zynq开发板,通常fpga部分称为PL端,ARM部分称为PS端。

2022.6.9

1.使用AD9516软件来配置一些寄存器信息,配置标准参考原理图上的一些输出要求来配置,具体使用方法还是得看资料;

2022.6.13

- TTL电平信号规定,+5V等价于逻辑“1”,0V等价于逻辑“0”(采用二进制来表示数据时)。这样的数据通信及电平规定方式,被称做TTL(晶体管-晶体管逻辑电平)信号系统。这是计算机处理器控制的设备内部各部分之间通信的标准技术。

2022.6.15

1.Vivado导入文件注释乱码时,可以使用Notepad++复制代码过来,转换不同的编码形式,再复制到Vivado中,

2022.6.16

1.Vivado仿真的时候,若波形蓝色zz表示高阻态,波形红色x表示未知态,注意是否赋予初值,或者是否进行连线数据处理等功能,

2.仿真的数据只与仿真文件有关,时钟的定义在仿真文件中,需要将代码联合起来的时候,可以创建一个top文件进行融合,让后再引入tb文件进行例化。(详情可以观看UART232案例)。

2022.6.17

1.在阅读芯片手册,配置引脚的时候,外设的初始化中默认为Default,

2022.6.20

- 脉冲宽度调制(PWM),是英文“Pulse Width Modulation”的缩写,简称脉宽调试。是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术。广泛应用在从测量、通信到功率控制与变换的许多领域中。

3.IP

4.项目的最终版本往往不带日期,修改版本命名有日期;

5.在设计一些电路的时候,通常将其在上电或断电期间设计为高阻抗状态,根据数据手册中的真值表等信息来设置,例如应将 OE 通过上拉电阻器接到 VCCA;

6. 闩(shuan)锁效应 (Latch-up)是CMOS集成电路中一个重要的问题,这种问题会导致 芯片 功能的混乱或者电路直接无法工作甚至烧毁。 闩锁效应是 CMOS工艺 所特有的寄生效应,严重会导致电路的失效,甚至烧毁芯片。 闩锁效应是由NMOS的有源区、P衬底、N阱、PMOS的有源区构成的n-p-n-p结构产生的,当其中一个三极管正偏时,就会构成 正反馈 形成闩锁。

2022.6.21

- VSS :S=series 表示公共连接的意思,通常指电路公共接地端电压 ;其中:对于数字电路来说,VCC 是电路的供电电压,VDD是芯片的工作电压(通常Vcc>Vdd) , VSS是接地点;

2.模拟电压输入常采用LC滤波电路,由电感加电容组成,电感对交流感抗大,通常一个电容管一个引脚,若引脚多可适当增加电容量;

3.VCC_1V0_PG,表示的并不是1V的电压输出,应该是电源输出的电压正常的一个标志,此时为5V,高电平;

4.电路图中设置的电阻为0Ω,是为了便于后期测试所设置,可直接连线短接;

2022.6.24

1.板子上电之前,需要先对电源进行测试,查看是否电源线对地短路,所以需要提前查看电源测试点,以及地线测试点;

2.测试前可以做一个excel表,统计需要测试的点,模板参考原理图审核点;

3.审核电路时也要注意其中的电流等参数是否正确;

4.D22和D28的6、42引脚需要飞线到VCC_1V0(TP19);

5.测试接地时可以参考J5的1、3、5、7、9、11、13等地;

2022.6.28

- Vivado中可以将部分代码封装成IP,方便以后调用。封装好IP以后,需要将IP的路径添加到工程中,然后才能在工程中被调用。

2022.7.4

1.绘制PCB时,可以根据模块来画,先在外板绘制好,再拖进板框;

2.通常PCB的过孔设置为内孔直径0.3mm,焊盘直径0.6mm;

2022.7.6

硬件调试步骤:

- 检测电源对地是否短路,先找到GND,注意GND是否隔离;无短路后再上电调试;

- 上电后检测电压,先看总电压,再看分电压,使用万用表时要注意先打GND,再打电源;

- 若总电源有电压,而LTM4644的二次电压无值,查看电阻是否接对;电压达不到预定值时也要查看是否电阻值正确;

- 通电后也要通过Vivado查看是否能够检测到芯片;

- 硬件调试完了以后,还需要为软件调试准备条件,比如网络线等来连接线,部分需要自己先焊接,后期再购买配备;

- 若发现封装连接位置反了,可以将连接的两个电阻交叉连接来解决。

2022.7.15

1.调试FPGA时,AD芯片给FPGA的实际电压可能与FPGA采到的电压并不一致,则需要通过芯片的时序图进行调整代码;慢量程为3.3V的电压,采集的数据用12位数据保留,则2的12次方为4096,通道采集的电压为采集的数值除以4096再乘3.3V;

2022.7.18

1.FPGA采集的电压与实际测的的电压,需要检测其是否有误差,根据采样值进行计算时,需要查看芯片手册,查看其参考电压是内部参考还是外部参考电压,根据设计者而定;

2022.7.21

1.FPGA常用的的IP有clk_wiz(时钟模块),可以设置多路时钟输出,设置时钟输入是单端输入还是差分输入,resetn是低电平有效还是高电平有效;

2.用于抓取测试点仿真的是ila模块,可以设计自己采集多少路信号,并要注意采集信号的位宽,例化时要注意与其一一对应;

3.有时候采样采不到,需要注意是否有足够的采样深度,如131072为较大的采样深度;

4.通常在顶层的ila只能抓取底层的输出信号,并不能随意抓取底层的任意信号,如要抓取底层信号,需要在底层例化ila,并抓取信号即可;若想抓取很多信号,可以在每一个底层都建立ila模块,采样的时候分窗口显示即可;

2022.7.25

1.在进行仿真时,如LED1秒翻转,我们采集信号时可能仿真波形看不见,所以需要我们手动更改一些参数,来进行仿真;

2.为保证工程的稳定性,我们可以将需要更改的参数例化进仿真文件,因此只需要在仿真文件中更改参数即可,而不会影响到原本的功能;

2022.7.28

1.AD画原理图时,若CS要取反,则可以输入C\S\,同理,若VSYNC要取反,则输入:V\S\Y\N\C\。

2022.8.1

1.AD9518的时钟配置:通常先根据用户需求,来选择芯片,根据VCO(MHz)的范围,如需要配置40M和136M,则通过其最小公倍数680的范围来找(防止后续配置输出出现小数而配置不成功),可以使用范围在1360,2040,2720范围左右的芯片,综合考虑成本以及其他需求后选择;

2.VCO主要通过R和N配置,其中N=P*B+A,配置时满足公式:REF/R=VCO/N,注意VCO为最小公倍数。100/10=2720/272,2720/17=40,2720/5=136

2022.8.4

- 带宽是指传感响应的幅频特性,即随着震动频率不同,响应输出幅度也不同,在某个频率时输出下降3dB,即带宽。但要将此时域数据序列不失真的重现出来,需要数据速率高于带宽的2倍。如带宽为80Hz,则数据速率须大于160Hz。

香农定理:

为了方便理解,假设我们采样的信号时域表示如下:f(t)=Asin(ωt)

也就是在频域中只含有一个频率的正弦信号。为了确定该正弦信号的幅值A和角速度ω(和频率对应),需要我们在一个周期内至少采样两个点,也就是说采样的频率要大于等于两倍的正弦信号的频率。推广至复杂的时域信号,就变成了采样频率要大于等于最大频率信号频率的两倍。

2022.8.22

1.前阵子都在对028项目的原理图进行设计,其在004接口控制板上进行了修改,根据修改后的协议进行设计;

2.首先,设计之前我们需要有个整体架构,板框分布,接插件距离FPGA的距离需要尽量短,故设计连线的时候需要考虑如何分配BANK,以及一些高速BANK的使用,其中也需要对每个BANK的支持电平进行分析,若信号为3.3V,接在了1.8V的BANK上,则需要进行电平转换;

3.信号线连接FPGA时,可以随便连接,大多数PIN支持差分信号L,注意时钟以及参考引脚的预留即可。

2022.8.23

原理图设计的规范化:

- 元器件的命名时,通常电源芯片为U?,其他集成芯片为D?,接插件为J?,变压器为T?

- 画原理图库时,各个引脚尽量做好分类,如AVCC,VCC,AGND,DGND等分类分布,这样会更美观,且连线会更加直观,方便原理图的查看;

- 画原理图时,尽量标注各个引脚的输入输出,进行原理图设计时会更加方便;

FPGA供电机制:FPGA芯片在正常工作的时候需要系统提供三套供电机制——外部端口供电机制、内部逻辑供电机制和专有电路供电机制。

- 外部端口供电机制:一般来说,FPGA会根据位置关系,将这么多的用户IO资源划分开来,形成若干的IO Bank,而每一个IO Bank具有单独的VCCIO接口资源。这意味了一片FPGA芯片的用户IO资源可以支持多种接口电平通信。例如,一个IO Bank的管脚与外部SDRAM芯片通过LVTTL3V3进行存储操作,而另一个IO Bank的管脚可以通过LVDS2V5的接口电平与外部高速差分接口进行通信。

- 内部逻辑供电机制:外部端口的供电一般电压要求较高,而对电流的要求较低,因为数字系统之间的通信不需要很强的电流驱动能力;而内部逻辑的供电一般供电电流较大,甚至可达十几安培,因此出于对功耗的控制,供电电压一般都比较低。由于以上的原因,不管一片FPGA芯片有多少个IO Bank,能支持多少个不同的VCCIO电平标准,一片FPGA芯片都只能有一个内部逻辑供电电源。VCCINT的管脚即为内部逻辑供电的管脚

- 专有电路供电机制:由于FPGA中不断集成了一些新的资源,而有些资源对电源的要求是比较特殊的,因此对于大多数FPGA芯片来说,还需要配合一些专有的电路供电机制来驱动这些资源可以正常工作。

- 例如,FPGA芯片中的PLL资源,由于其主要还是利用的模拟电路的特性来实现的,模拟电路对电源噪声远比数字电路敏感,因此,FPGA中的PLL资源一般需要专门的供电电路来供电,而FPGA自然也会为之提供相应的供电管脚,例如名称类似VCCPLL的。

2022.8.30

前段时间都在检查原理图设计,并对其进行了修正

- 时钟信号通常比较敏感,故尽量不要用接插件外接提供;

- 外接电路时,若不清楚接多少阻值的电阻和电容,可以接两个电阻,增大容错,方便后期修改;

- 使能比较多的芯片,通常可以只拉高或拉低一个引脚使其不工作,其余引脚拉高或拉低到正常工作模式;但是最好都连接到FPGA上,由FPGA辅助控制;

- 不清楚接法的电路一定要参考原理图设计,通常在芯片手册里,若没有则在官网找原理图设计;

- 不同通道输出的外接电路可能不同,一定要细致,出必有因;

- 引脚高低电平可能影响芯片的工作模式,故设计时应该考虑好芯片的工作模式;

2022.9.15

因为成都疫情,居家隔离了半个月,解封就继续上班学习。

- FSMC(Flexible Static Memory Controller,可变静态存储控制器)是STM32系列中内部集成256 KB以上FlaSh,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。之所以称为“可变”,是由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据/地址/控制信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产品体积以及成本的综合要求。

- FSMC内部结构。STM32微控制器之所以能够支持NOR Flash和NAND Flash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR Flash和NAND/PC Card两个控制器,分别支持两种截然不同的存储器访问方式。在STM32内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M3,另一端则是面向扩展存储器的外部总线。内核对外部存储器的访问信号发送到AHB总线后,经过FSMC转换为符合外部存储器通信规约的信号,送到外部存储器的相应引脚,实现内核与外部存储器之间的数据交互。FSMC起到桥梁作用,既能够进行信号类型的转换,又能够进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

- NAND flash和NOR flash的区别详解:见CSDN收藏(电子设计)

2022.9.16

- 画原理图库时,引脚的order表示位置,与number并无关系,故可以有差异;

- 通常芯片的封装比较混乱,需要自己根据需要进行调整,按照引脚的功能进行分类,一方面可以使原理图更加美观,同时也更能够被人读懂,也可以参考现有的一些demo进行设计。

- 磁珠和电感的区别

磁珠由氧磁体组成,电感由磁芯和线圈组成,磁珠把交流信号转化为热能,电感把交流存储起来,缓慢的释放出去,因此说电感是储能元件,而磁珠是能量转换(消耗)器件。电感多用于电源滤波回路,磁珠多用于信号回路,磁珠主要用于抑制电磁辐射干扰,而电感用于这方面则侧重于抑制传导性干扰。两者都可用于处理EMC(电磁兼容)、EMI(电磁干扰)问题。磁珠是用来吸收超高频信号,例如一些RF电路、PLL、振荡电路、含超高频存储器电路(DDR SDRAM,RAMBUS等)都需要在电源输入部分加磁珠,而电感是一种蓄能元件,用在LC振荡电路、中低频的滤波电路等,其应用频率范围很少超过50MHZ。地的连接一般用电感,电源的连接也用电感,而对信号线则常采用磁珠。

2022.9.19

- DCMI是STM32F4芯片自带的一个数字摄像头接口,该接口是一个同步并行接口,能够接受外部8位、10位、12位、14位CMOS摄像头模块发出的高速数据流;

- STM32中的ETH为以太网(Ethernet),

MII接口:介质独立接口,定义了10 Mbit/s 和100 Mbit/s 的数据传输速率下MAC 子层与PHY 之间的互连,

RMII接口:Reduced media-independent interface: RMII(精简介质独立接口)。精简介质独立接口(RMII) 规范降低了10/100 Mbit/s 下微控制器以太网外设与外部PHY 间的引脚数。 - I2S(Inter—IC Sound)总线, 又称 集成电路内置音频总线。

2022.9.20

- FIFO:是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO的一些重要参数如下 - FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

- FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。在一个具体的应用中也不可能由一些参数算数精确的所需FIFO深度为多少,这在写速度大于读速度的理想状态下是可行的,但在实际中用到的FIFO深度往往要大于计算值。一般来说根据电路的具体情况,在兼顾系统性能和FIFO成本的情况下估算一个大概的宽度和深度就可以了。而对于写速度慢于读速度的应用,FIFO的深度要根据读出的数据结构和读出数据的由那些具体的要求来确定。

- 满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出(overflow)。

- 空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,以阻止FIFO的读操作继续从FIFO中读出数据而造成无效数据的读出(underflow)。

- 读时钟:读操作所遵循的时钟,在每个时钟沿来临时读数据。

- 写时钟:写操作所遵循的时钟,在每个时钟沿来临时写数据。

- 读指针:指向下一个读出地址。读完后自动加1。

- 写指针:指向下一个要写入的地址的,写完自动加1。

- 读写指针其实就是读写的地址,只不过这个地址不能任意选择,而是连续的。

2022.9.23

- SWDIO:JTAG:Test Mode State pin ; SWD: Data I/O pin 数据线;

- SWCLK:JTAG: Test Clock pin ; SWD: Clock pin 时钟线;

- AD中PCB根据位号搜索,快捷键:E->J->C

2022.9.24

1.电压进行转换后的输出电流不能太小,否则不能驱动后续的电路,后续电路相当于并联分流,各电路需要的电流是通过其自身系统的负载决定的,用多少取多少。

2022.9.26

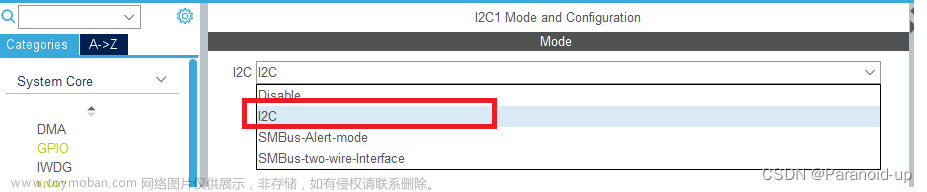

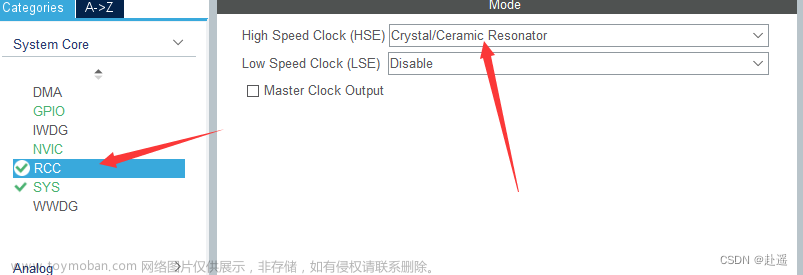

1.在使用STM32cube时,配置了一些引脚后,有黄色三角形感叹号提示,这个警告的意义在于提醒开发者当你选择了引脚某功能后,会限制其他category 的部分功能。

这种警告就是说一个管脚有多个可能的作用,你选择了一个之后,其他不能选,用一个警告三角形提示你。仅仅为提示,不是报错或者警告。

2022.10.8

1.国庆节的时候,外出调试三天,首先大致学会了频谱仪的简单使用,射频工程师用的很多,主要设置自己观察信号的中心频率,并设置其扫描范围,用探针观察信号的时候,用Peak Search查找尖峰频率,并保持。再通过信号源改变幅度,db,调试到利于观察的位置。

2.对于一些模拟输入,不能接入BUFFER中,要么将模拟信号通过ADC转为数字信号再接入MCU,或者直接将模拟信号接入MCU的硬件ADC引脚

2022.10.12

1.根据间距大致可分为2.54mm,2.00mm,1.27mm,1.00mm,0.8mm五类根据排数有单排针,双排针,三排针等;根据封装用法则有贴片SMT(卧贴/立贴),插件DIP(直插/弯插)等;按照安装方式划分:180°用S表示、90°用W表示,SMT用T表示。

2022.10.13

1.安装柱(螺丝位置),在整车有功率源的情况下,安装孔不需要添加网络,不能接地,防止有干扰;

2.通用螺丝孔的型号为M4;

3.在处理电磁兼容等情况时,信号等线路常常使用双绞线,且端口裸露出来的长度不能高于10多mm;

2022.10.19

1.PCB沉金:

一、 什么是沉金呢?

简单来说,沉金就是采用化学沉积的方法,通过化学氧化还原反应在线路板表面产生一层金属镀层。

二、为什么要沉金呢?

电路板上的铜主要是紫铜,铜焊点在空气中容易被氧化,这样会造成导电性也就是吃锡不良或者接触不良,降低了电路板的性能。

那么就需要对铜焊点进行表面处理,沉金就是在上面镀金,金可以有效的阻隔铜金属和空气防止氧化掉,所以沉金是表面防氧化的一种处理方式,是通过化学反应在铜的表面覆盖上一层金,又叫做化金。

四、采用沉金板的的线路板有哪些好处?

1、沉金板颜色鲜艳,色泽好,卖相好看。

2、沉金所形成的晶体结构比其他表面处理更易焊接,能拥有较好的性能,保证品质。

3、因沉金板只在焊盘上有镍金,不会对信号有影响,因为趋肤效应中信号的传输是在铜层。

4、金的金属属性比较稳定,晶体结构更致密,不易发生氧化反应。

5、因沉金板只有焊盘上有镍金,所以线路上的阻焊与铜层的结合更牢固,也不容易造成微短路。

6、工程在作补偿时不会对间距产生影响。

7、沉金板的应力更易控制。

2020.10.20

1.项目对接:在有外协合作的时候,一定要对接好,多联系。比如接插件的部分,尽量对接采用相同规格,若因为各方原因达不到要求,需要采用焊接技术,则需要考虑接线是否能承受焊接,是否容易焊断等问题。

2.反思:在这次项目中,由于缺乏主观判断能力,听取了焊接接线的要求,且不知道1.27mm的排线承受不了焊接,导致在PCB设计完成后仍需要修改封装,且要重新采购,为众多人带来了麻烦,实为不该犯的错误。在今后的设计中,一定要更加严谨,在自己不知道的情况下,需要多问,听取他人的建议。居安思危,一定要保持怀疑态度,排除潜在隐患,方能走的长远!

2022.10.21

1.电路原理图:SCH;电路板:PCB;印刷电路板:裸板没有上元器件的电路板;IC板:有集成电路零件装载

2022.10.24

1.选择电源转换时,注意查看芯片的输出电压范围,例如:

LTM4644:Operating over an input voltage range of 4V to 14V or 2.375V to 14V

with an external bias supply, the LTM4644/LTM4644-1 supports an output voltage range of 0.6V to 5.5V.(输出电压最高为5.5V)

LTM4643:Operating over an input voltage range of 4V to 20V or 2.375V to 20V with an external bias supply, the LTM4643 supports an output voltage range of 0.6V to 3.3V each set by a single external resistor.(输出电压最高为3.3V)

2022.10.25

- 知道运放的特点都是高输入阻抗,低输出阻抗;而假设的理想运放更是将输入阻抗近似到无穷大,输出阻抗趋近于零;高输入阻抗是为是减小对前级的影响,而低输出阻抗带负载能力强,所以在小信号放大电路中我们总是在前级设计一个跟随电路,提高电路的性能。由于高输入阻抗,差模输入阻抗非常高,输入偏置电流非常小,一般rid>1GΩ~1TΩ,IB为几皮安到几十皮安。

2022.11.6

1.通过对ADDD-2020004_SUB04的板子的调试,3V3短路,发现由于是STM32F407的封装画错,其中99脚的VSS引脚画为PDR_ON,误将其拉高。实则应该接地,才导致3V3与地短路,将其99脚翘起来再飞线到GND后解决。经过这次经验,得出结论,不要轻易参考网上的原理图,最好找有权威性的官方文档,画原理图时应该细致到每一个引脚,需要其一一对应。只有严谨的态度,才能减少调试问题。

2.其中3V3电压转换后为3.9V,排查后发现是1.5k的电阻误焊为1.15k,电阻装反袋子导致。调试的时候需要保持怀疑,确保元器件的正确性,防止走弯路。

3.在软件调试的时候,最好先参考官方的设计PDF,理解了代码的区别才能做好修改,不要直接上手改代码的引脚。例如:其中 LCD_BASE,必须根据我们外部电路的连接来确定,我们使用 Bank1.sector4 就是从 地址 0X6C000000 开始,而 0X0000007E,则是 A6 的偏移量,这里很多朋友不理解这个偏移量 的概念,简单说明下:以 A6 为例,7E 转换成二进制就是:1111110,而 16 位数据时,地址右 移一位对齐,那么实际对应到地址引脚的时候,就是:A6:A0=0111111,此时 A6 是 0,但是如果 16 位地址再加 1(注意:对应到 8 位地址是加 2,即 7E+0X02),那么:A6:A0=1000000,此 时 A6 就是 1 了,即实现了对 RS 的 0 和 1 的控制。

由于我们配置的为A16,故·A16:A0=0 1111 1111 1111 1111,(对其加一,则A16:A0=1 0000 0000 0000 0000,实现了对RS的0和1的控制),由于其为16位,地址右移一位后才为0FFFF,故其移位前为:1 1111 1111 1111 1110=1FFFE,故其地址偏移量为0X0001FFFE。

2022.11.28

1.这个月主要就是对板子进行调试,幸运的是都调通了,只有前面封装引起的错误,导致了重新投板,增加了研究成本;

2.对于调试的模块,大多根据正点原子官方例程,进行引脚修改,并代码修改后完成,分别有:

a) 电源转换模块:通过匹配电阻值(2.59k,1.5k),用LT1963AES8将5V电压转换为3.3V;

b) ADC模拟电压采集模块:适用的是STM32的ADC引脚,采集的是外部的电压值,精度较高;

c) 数字量输出模块:输出高低电平(3.3V/0V),以给后续电路,有时无法驱动后续电路则需要查看驱动电流是否合格;

d) EEPROM,Flash:根据历程修改,且IIC以及SPI引脚应该适用硬件将其上拉,若硬件未上拉,则需要软件上拉;

e) CAN通信:需要上位机发送CAN数据,且能通过上位机读取芯片发送的CAN数据;

f) 晶振:32.768KHz的晶振供给内部RTC时钟,用于实时显示时间,参考官方例程;

g) 数字量输入模块:用HAL函数直接读取引脚输入的高低电平即可;

3.对于结构问题,在设计的时候需要同结构工程师沟通好,防止后续上整机的时候有误差。例如:LCD屏幕到板子间的距离,除了大概了解距离外,还应该在板子回来以后,再次实物测量,再次核对,防止结构出错。

4.对于板子温度问题,当整机上有发热模块时,一定需要处理好板子的隔热,通常一些芯片的耐温性能并不好,例如晶振焊接时,若引脚烫的时间过长,通常会烧坏晶振,以32.768KHz直插型为例,要求使用178°C熔点的焊锡,晶振内部的温度超过150°C,会引起晶振特性的恶化或者不起振。解决办法:焊接制程过程中一定要规范操作,对焊接时间和温度的设定要符合晶振的要求。引脚焊接的正确方式应是:不在晶振引脚的根部直接焊接(将两脚的焊盘烫化以后,将引脚插入焊锡里面,而不能直接烫引脚,防止烧坏);280°C下焊接时间为5秒以内,260°C下焊接时间为10秒以内。同时,各个芯片的温度限度也应严格把控,STM32F407VET6的工作温度在-40℃-85℃之间,故环境温度不能太高。

2022.11.29

1.ZI Data: zero initialized data,零初始化的可读写变量Shows how many bytes are occupied by zero-initialized data.0数据段,存放未初始化的全局变量及初始化为0的变量。

存储Size:

RO size: Code + RO_data,表示程序占用Flash空间的大小。

RW size: RW_data + ZI_data,表示运行时占用RAM的大小。

ROM (minimum)size = Code + RO_data + RW_data (即烧/下载程序到FLASH/ROM时,所占用的最小空间)

Total ROM Size (Code + RO Data + RW Data)这样所写的程序占用的ROM的字节总数,也就是说程序所下载到ROM flash 中的大小。

2022.12.5

1.NCO:数字控制振荡器(NCO,numerically controlled oscillator)是软件无线电、直接数据频率合成器(DDS,Direct digital synthesizer)、快速傅立叶变换(FFT,Fast Fourier Transform) 等的重要组成部分,同时也是决定其性能的主要因素之一,用于产生可控的正弦波或余弦波。随着芯片集成度的提高、在信号处理、数字通信领域、调制解调、变频调速、制导控制、电力电子等方面得到越来越广泛的应用。

2. 开关电源(DC/DC)和线性电源(LDO低压差线性稳压器)的区别:

a) 开关电源是直流电转变为高频脉冲电流,将电能储存到电感、电容元件中,利用电感、电容的特性将电能按预定的要求释放出来来改变输出电压或电流的; 线性电源没有高频脉冲和储存元件,它利用元器件线性特性在负载变化时瞬间反馈控制输入达到稳定电压和电流的;

b) 开关电源可以降压,也可以升压;线性电源只能降压;

c) 开关电源效率高;线性电源效率低;

d) 线性电源控制速度快,波纹小;开关电源波纹大;

参考博客:开关电源(DC/DC)和线性电源(LDO低压差线性稳压器)的区别_国产运算放大器_模拟开关_线性稳压器_电平转换器_小逻辑_比较器_电压基准源_江苏润石官网 (run-ic.com);

2022.12.6

1.PCB设计中电流与线宽的关系: PCB的载流能力取决与以下因素:线宽、线厚(铜箔厚度)、容许温升。大家都知道,PCB走线越宽,载流能力越大。

经验公式计算:0.15×线宽(W)=A。

2. 阻抗匹配

具有电阻、电感和电容的电路里,对交流电所起的阻碍作用叫做阻抗。阻抗常用Z表示,阻抗的单位是欧。对于一个具体电路,阻抗不是不变的,而是随着频率变化而变化。类似于向墙上扔皮球,要把皮球传过去,但是墙是硬的,会弹回来,如果是扔到窗帘上就不会弹回来,阻抗的意义就是让发射,接收,传输过程中能量都是一致的衰减程度,不会有能力反射,向皮球一样,连续不断地向墙上扔皮球,如果有皮球弹回来,就会和正在扔过去的皮球撞上,这就类似于一个方波信号在取反的时候有毛刺震荡。

阻抗匹配则传输功率大,对于一个电源来讲,当它的内阻等于负载时,输出功率最大,此时阻抗匹配。阻抗匹配是指在能量传输时,要求输出阻抗,负载阻抗要和传输线的特征阻抗相等此时的传输不会产生反射,这表明所有能量都被负载吸收了。高速 PCB布线时,为了防止信号的反射,通常要求是线路的阻抗为单端50欧姆,差分100欧。

2022.12.8

1.对于我们测试的时候,一定要佩戴静电手环,或者静电手套,因为冬季,很容易产生静电,而人体静电可达几千伏甚至几万伏,很容易击穿元器件。案例:可能由于未佩戴静电手环,导致在烧录程序的时候,插拔接插件时,由于静电,将JTAG调试引脚击穿,而无法再烧录程序,是一种不可挽回的损失。

2.对于我们检测硬件时,可以通过万用表打通断,查看一些芯片非地引脚是否对地短路,或者各个引脚是否相互短路。若检测没有问题,可以通过使用万用表的电阻挡位,将两个板子(问题板/正常板)的引脚进行对比,查看一些高阻引脚是否电阻过低,是否电阻有差异。

2022.12.9

1.MSB( most significant bit):最高有效位,指的是一个n位二进制数字中的n-1位,具有最高的权值2^(n-1);

LSB( least significant bit):最低有效位,指的是一个二进制数字中的第0位(即最低位);

2022.12.12

- 由于LVDS信号电平变化在0.85-1.55V之间,其由逻辑低电平到逻辑高电平变化的时间比TTL电平要快得多,所以LVDS更适合用于传输高速变化信号。其低压低电流,噪声低功耗也低。 多用于板内信号传输。

LVDS使用注意:速率可以最快可达到600M以上,对PCB布线要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm)。100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。

2022.12.20

- DDR3是一种内存规格,它是SDRAM家族的内存产品。DDR3之前的产品有DDR和DDR2。DDR(Double Data Rate)是双倍速率同步动态随机存储器,严格的说DDR应该叫DDR SDRAM。DDR2是DDR产品的升级产品,它是四倍速率同步动态随机存储器。DDR3在DDR2的基础上实现了更高的性能(增加到八倍)和更低的电压。

2023.1.30

不知不觉已经很久没有记录了,主要是前段时间逐步开始学FPGA,遇到的问题大都收藏在了博客,写日志的话会既浪费篇幅,也不能更直观的理解,以后,会继续对一些比较简短且有用的东西进行记录,包括硬件以及FPGA。

- IP核工作必须要满足一定的时序要求,所以需要将数据按照一定时序送入IP核。IP核交互是用AXI-Stream接口,关于AXI-Stream接口的时序可自行查一些相关资料,这里不做详细介绍。简言之,AXI-Stream接口分为主机(master)和从机(slave),主机为发起端,从机为响应端,只有ready信号和valid信号同时为高时数据才能被有效写入或读出。举个例子,主机检测从机发出的ready信号,当为高时将valid信号拉高即可从从机读出或向从机写入数据。

- 在测试FFT(快速傅里叶变换),输入可以通过Matlab画图,到处波形的数据,通过仿真文件读取数据,作为输入波形。生成波形的时候在Matlab也进行了仿真(用了傅里叶变换函数),所以,能进行较好的结果对比。

2023.2.3

- 元件引脚直径与PCB焊盘孔径对应关系:

2023.2.15

PCB拼板

-

为什么要拼板?

a.为了满足生产的需求。有些PCB板太小,不满足做夹具的要求,所以需要拼在一起进行生产。

b.提高SMT贴片的焊接效率。只需要过一次SMT即可完成多块PCB的焊接。

c.提高成本利用率。有些PCB板是异形的,拼板可以更高效率的利用PCB板面积,减少浪费,提高成本的利用率 -

拼板的方式

PCB拼板方式-V割(V-CUT)

V割,又称V-CUT,在规则板中使用较多。V割是在两个板子的连接处画一个槽,只要将两个板子拼在一起,之间留点空隙即可(一般0.4mm),但这个地方板子的连接就比较薄,容易掰断,拼板时需将两个板子的边缘合并在一起。V割一般都是直线,不会有弯曲圆弧等复杂的走线,在拼板时尽量在一条直线上,V割线可以使用2D线放在所有层进行表示。

PCB拼板方式-邮票孔

对于不规则的PCB板,比如圆形的,V割是做不到的,这个时候就需要使用到邮票孔来进行拼板连接,因此邮票孔一般在异形板中使用的较多。在两个板子的边缘通过一小块板材进行连接,而这一小块板材与两块板的连接处有许多小孔,这样容易掰断。掰断之后板子的边缘像邮票的边缘,因此这种拼板方式被称为邮票孔。

PCB拼板方式-空心连接条

空心连接条在有半孔工艺的板子中使用较多,是使用很窄的板材进行连接,和邮票孔有些类似,区别在于连接条的连接部分更窄一点,而且两边没有过孔。空心连接条的拼板方式有一个缺点:板子掰开之后会有一个很明显的凸点。邮票孔也有凸点,因为被过孔分开所以不怎么明显。有人可能会觉得直接用邮票孔不就好了,为啥还要用空心连接条?这是因为在做四周都是半孔模块的时候,邮票孔和V割都无法使用的,只能通过空心连接条在模块四个角进行连接。

2023.2.24

-

FPC简介

FPC即柔性电路板,是PCB的一种。

按层数划分, FPC 可分类为单层 FPC、双层 FPC、多层 FPC;相关制造技术以单层 FPC 制造技术为基础,通过迭层压合技术实现,具体如下:相比普通PCB,FPC具有配线密度高、重量轻、厚度薄、可折叠弯曲、三维布线等其他类型电路板无法比拟的优势,因此应用广泛。 -

放大器(简称“运放”)是具有很高放大倍数的电路单元。运算放大器是一个内含多级放大电路的电子集成电路。分别是输入级,中间级,发大级还有偏置电路。

-

线性放大器IC各种电子产品不可缺少的部分,如何设计出高质量的电子产品,除了要求总体方案最佳外,放大器设计得是否合理可靠直接影响整个电子产品的系统性能

2023.3.2

- 在使用NXP的Kinetis系列的KV1X的MCU时,此款芯片只有SWD调试接口,在使用kei调试和下载过程中时不时会找不到SWD接口或者芯片被锁住,检查电源稳定纹波很小,NMI已上拉10k电阻,可以在jlink Command中找到内核并解锁。在恩智浦论坛上询问FAE,芯片内部DIO已上拉,SCK已下拉,可能是jlink到SWD接口的连接线较长导致信号不稳定,或者是Layout做的太差,引起芯片被锁,建议SWD_DIO上拉10k电阻,SWD_SCK下拉10K电阻保证信号的稳定性。按照建议做了第二版后,调试的稳定性增强,被锁或找不到接口的情况基本不再出现。

在画板时可预留上下拉电阻的位置,在出现这种情况后方便调试。 - Modelsim和vivado有版本匹配问题,版本不匹配就会编译失败。

vivado2018.2与modelsim10.7匹配

vivado2017.4与modelsim10.6匹配,

非常抱歉,小半年没有更新了,其中也是零星的记录了一些,前段时间主要搞嵌入式软件耽搁了很多时间,这阵子又陆陆续续开始画板子,才开始记录。感谢兄dei们的提醒,才让我想起了初心,需要不断积累,不断记录,才能进步!

2023.3.29

1,最近工作任务中心在写代码上,主要是基于STM32F103的芯片,实现的功能有:ADC的温度采集,数字量输入采集,与数字量输出控制,实现422串口通信,以及CAN通信,同时运用了定时器以及中断等功能,对单片机的学习又加深一步;

2,OBC(on board charge)准确来说是“车载充电器”。一般是低功率充电机。分为车载有线充电和车载无线充电。

DCDC(DC-DC converter),直流电压转换成另一个直流电压的装置。

BMS的全称为电池管理系统 (Battery Management System), 即管理电池的充放电,使电池处于一个最佳的状态。

2023.4.4

1,最近在整机调试,遇到一些问题,比如CAN通信不能控制,在软件找不到问题的情况下,首先检查CAN_H和CAN_L连线是否正确,将CAN线并联接线通过CAN上位机抓取CAN信号,查看是否有信息传输;

2,测试232转422的串口盒时,采用回环模式,同时,要查看是否需要单独供电,有一些是电源适配器供电,有的需要电源接线24V供电,串口上位机是否波特率匹配等。

2023.4.13

1,测试时发现一个问题,对面给我们3.3V,连接上发现实际我们的数字量输入电压为1.7V左右(处于STM32门限电平接线,容易在0和1中间跳变),原因是由于上级数字量输出引脚进行了上拉,其中有个上拉电阻,我们也加入了下拉电阻,导致分压,将电压拉低。所以以后设计时,需要进行沟通,确认是否进行了上下拉。

2023.4.21

1,硬件调试完以后,被抓壮丁去写了软件,最近都在写单片机的软件,其中学会了使用很多东西,比如串口中断接收,CAN中断接收,定时器的使用,以及根据通信协议进行逻辑代码的书写。单片机代码写一写还是很有用的。

2,在写串口通信时,要求写一个校验和,可以增加信息的准确率,原理如下:

发送方:对要发送的数据进行累加,得到一个数据和,对和求反,即得到我们的校验值。然后把要发的数据和这个校验值一起发送给接收方。

接收方:对接收的数据(包括校验和)进行累加,如果得到0(关于网上说这里需要加1,本人通过测试发现,不需要累加),那么说明数据没有出现传输错误。(注意,此处发送方和接收方用于保存累加结果的类型一定要一致,否则加1就无法实现溢出从而无法得到0,校验就会无效)。

2023.5.4

1,Cadence如何将原理图输出为PDF文件:

- 在打印机设置中(Print Setup),打印机不要选择Microsoft Print to PDF,可以选择Adobe PDF

- 选中.DSN文件(表示打印所有页)

- 打开Print选项

- Scale选项中:勾选Scale to paper size

- Print Option选项中:勾选Inst.Mode(Preferred)

- 点击OK开始打印

若想用Microsoft Print to PDF进行打印,步骤如下: - 在打印机设置中(Print Setup),打印机不要选择Microsoft Print to PDF,可以选择Adobe PDF

- 选中.DSN文件(表示打印所有页)

- 打开Print选项

- Scale选项中:勾选Scaling

- Print Option选项中:勾选Inst.Mode(Preferred)

- Setup选项中:将打印机修改为Microsoft Print to PDF

- 点击OK开始打印

2023.5.11

最近新设计的板子,集成了继电器的驱动电路,所以,学习了一下继电器的工作原理,以及如何使用光耦隔离,加上三极管,或者场效应管来驱动继电器。

1, 继电器:电磁继电器(electromagnetic relay)是一种电子控制器件,它具有控制系统(输入回路)和被控制系统(输出回路),通常应用于自动控制电路中,它是用较小的电流、较低的电压去控制较大电流、较高的电压的一种开关控制方式,在电路中起着自动调节、安全保护、转换电路等作用。我们实际用处大多数就是拿来当作开关,通断一些较高的电压。同时,以后继电器选型需要考虑尖峰脉冲,耐压值,以及冲击电压等,防止继电器的反向电压对我们的电路进行损坏。

如上图所示,我们接继电器通常有两根线,一根是为线圈供电的线(红线),通常是一个较大的电压,比如24V或者12V,另外一根线则是用来控制线圈供电是否导通到地形成回路的线。

我们通常使用的继电器如下图所示(用于大电源的开关控制):

具体工作原理如下:

如上图,矩形为继电器,且三级管的地必须为12V的地,这样在三极管导通的时候,12V才能接到地,形成回路,线圈闭合,继电器正常工作。上图中的D1是为了减小继电器开关闭合过程中形成的反向电动势,对我们的三极管进行冲击。也可以加入肖特基二极管,改善效果更好。

2, 光耦:

光耦一般用于信号的隔离。当两个电路的电源参考点不相关时,使用光耦可以保证在两边不共地的情况下,完成信号的传输。

光耦的基本原理

光耦的原理图如下所示

其内部可以看做一个特殊的“三极管”;一般的三极管是通过基极B和发射极E间的电流,去控制集电极C和发射极E间的电流;而光耦可以看做是用输入端的发光管的光强度在控制输出端的电流;而输入端的发光管是个二极管,也就是用输入端的电流去控制输出端的电流,功能上和三级管是等效的,而由于中间的控制是靠光传输,所以输入端和输出端可以没有固定的电压差,也即相互隔离。将大电压和小电压进行隔离,防止进行干扰,以及不当操作烧毁芯片。在这插一句,据说,光耦对温度比较敏感,自身也比较脆弱,在焊接的过程中,要防止烙铁长时间接触,以免烫坏芯片(以前就烫坏过晶振0.0)。

以下是找的一个继电器驱动电路原理图:

当VALVE2为高电压,三极管Q13导通,则光耦U13导通,同时U13的4脚和3脚导通,继电器的5V接到地,线圈导通,继电器工作。

以上就是光耦,和三极管,来组合驱动继电器的工作原理,在以后的设计中,大同小异,举一反三。在选型过程中,一定要注意,电流能否驱动,驱动继电器的电流一定要选大的,比如这次设计中,这个继电器虽然只要250mA的驱动电流,但是苟老师也选了一个4A的场效应管来驱动,不清楚后续是否会有问题,等以后调试再看(后续调试发现没什么问题,能够正常驱动,但是可以将R46的电阻稍微调小一些,需要考虑光耦的驱动电流问题,具体参考各个光耦的参数型号)。

2023.6.1

1,漏极开路(Open Drain)即高阻状态,适用于输入/输出,其可独立输入/输出低电平和高阻状态,若需要产生高电平,则需使用外部上拉电阻。

2,高阻状态:高阻状态是三态门电路的一种状态。逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。电路分析时高阻态可做开路理解。

3,I2C 总线在物理连接上非常简单,分别由SDA(串行数据线)和SCL(串行时钟线)及上拉电阻组成。通信原理是通过对SCL和SDA线高低电平时序的控制,来产生I2C总线协议所需要的信号进行数据的传递。在总线空闲状态时,SCL和SDA被上拉电阻Rp拉高,使SDA和SCL线都保持高电平。

4,I2C通信方式为半双工,只有一根SDA线,同一时间只可以单向通信,485也为半双工,SPI和uart通信为全双工。

5,模拟射频线的隔层参考

大家都知道我们在做PCB设计的时候,射频线一般都是不打孔换层的,一般直接都是走的器件层,而我们处理它的常用方法可能就是加粗走线,然后掏空参考层,在它的下下层给铺地做参考。那么为什么会這么走呢?

因为射频走线也是控制50欧姆的阻抗,一般50欧姆阻抗表层走线是6-7mil线宽的样子,但是呢,射频线对信号质量要求很高,考虑到抗干扰,衰减及趋肤效应等方面原因,加粗走线是很有必要的。但是一旦加粗走线,我们的阻抗就会变小如果还是参考他的相邻层的话,所以我们就要想办法将它的阻抗给提上去,而线到参考层的距离越大阻抗就会变大,所以我们会掏空相临层然后让他参考下一层。

2023.7.3

1,ICD(Interface Control Document)称为接口控制文件;

2,Cadence绘制原理图时,若有要求,需要统一页面模板,在库文件中有,可引用;

3,LVTTL(LowVoltage Transistor-Transistor Logic)

LVTTL电平标准即低电压三极管-三极管逻辑电平标准是EIA/JESDSA的一种通用的3.3V电平标准,该标准的输入输出供电电压(VCCO)为3.3V,不需要参考电压(VREF)和终端电压(VTT);

2023.7.13

1,今天在选择LDO电源芯片的时候,发现dropout voltage(压差)是LDO最常见的参数之一,但是并不是所有的工程师都能够正确的设计LDO dropout voltage,导致产品可靠性具有隐患,降低平均无故障时间。和DCDC开关电源架构不同,LDO内部的管子是工作在放大状态的,在这样的大前提下,LDO输入输出必须要满足一定的压差条件,LDO才能有效进行反馈调节,正常工作。

2,LDO内部影响Dropout Voltage的几个原因,指导大家来正确选型。LDO内部除了基本的LDO控制电流外,往往还有一些保护电路、放电电路、逻辑控制电路等,有的LDO内部还有电荷泵等接口,这些电路都是要吃电的,所以IC的dropout voltage除了考虑内部管子的工作状态之外,还要考虑内部其他电路的供电需求。

3. 即使LDO输入电压可以是1.14V,输出是1V@Iout=300mA,我们也不能直接选择1.14V的电源提供给LDO。

4,第二个必考虑因素,走线。

我们举“栗”说明,DCDC输出1.14V;负载需求,1V@Iout=300mA。下图是线路损耗拆解,在走线100mΩ的情况下,如果要满足负载1V@Iout=300mA的需求,则留给LDO的dropout voltage只有0.08v,无法满足0.14V的规格,设计也无法保证性能和稳定性。

我们在走线时就要控制好走线的DCR,有必要仿真管控。

200mΩ * 300mA = 0.06V;1.14 – 0.06 – 1 = 0.08<0.14V(不满足压差条件)

5,第三个因素是前置电源的纹波影响。

一般为了降低功耗,LDO前级选择DCDC开关降压电路,BUCK工作时会有纹波,使得LDO输入电压会有最低值,由于电容的存在,这一点的影响不是特别大,只有在极个别情况下才会考虑这点。

2023.7.26

1,Xilinx FPGA中HP HR HD bank分别是什么用途

7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Bank和HD Bank,但并不是一个FPGA中会同时包含HP/HR/HD Bank。

• HP:High Performance

• HR:High Range

• HD:High Density

HP Bank,从名字就可以看出来,应用于高性能也就是速度比较高的场景,比如DDR或者其它高速差分总线(不是gtx),由于速率比较高,Bank电压最高也只能到1.8V。

HR Bank表示支持wider range of I/O standards,最高能够支持到3.3V的电压。

HD Bank应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V

Kintex UltraScale 和Virtex UltraScale中有HP Bank和HR Bank,Virtex UltraScale+系列中只有HP Bank,Zynq UltraScale+ MPSoC 和Kintex UltraScale+ 系列包含HP和HR Bank。

由于应用场景不同,支持的IO原语也有差异,下图是7系列FPGA HP Bank和HR Bank支持的特性:

下图是UltraScale系列FPGA HP Bank和HR Bank支持的特性:

HD Bank由于相对特殊一些,单独列了出来:

2,MRCC和SRCC的区别

只有7系列的FPGA中才有MRCC和SRCC的说法,到了UltraScale系列,都是叫GC。

看了上一篇文章的同学应该清楚MRCC就是Multi Region的CC,从该管脚输入的时钟可以access到不同的clock region,而SRCC就是Single Region的CC,从该管脚输入的时钟只能access当前clock region。

所以有同学就会觉得,如果想使用全局时钟,就必须将时钟接到MRCC,而不能是SRCC。但这种理解是错误的,下面我们会详细解释。

手册中对MRCC驱动多个clock region的说明如下:

MRCCs can access multiple clock regions and the global clock tree. MRCCs function the same as SRCCs and can additionally drive multi-clock region buffers (BUFMR) to access up to three clock regions.

MRCC通过BUFMR来access最多三个clock region,从下面的图也可以看出,已经用红色的线将MRCC的路径都标出来,可以看到,MRCC通过了BUFMR到达了CMT Backbone(如果对CMT Backbone不理解,可以看前面两篇文章),然后就可以access其他的clock region了。

从上面这个图可以看出,MRCC可以直接驱动BUFR和BUFIO,也可以先经过BUFMR后再驱动BUFIO和BUFR。

SRCC的路径在下面的图中用红色的线标识出来,可看到,它的路径只在当前的clock region里面。

An MRCC pin pair can drive a specific BUFMR, which in turn can drive BUFIOs and BUFRs in the same and adjacent regions facilitating multi-region/bank interfaces. Similarly, a GT quad can also drive the BUFMRs.

下面这个表格解释的就更加清晰了,MRCC和SRCC都是由外部的时钟驱动,而且MRCC和SRCC的区别就在于MRCC可以驱动BUFMR,SRCC不行。其他基本都一样,它们都可以驱动四个BUFIO、四个BUFR、一个CMT、上下相邻的CMT、16个BUFG和BUFH。 其中有一点很关键,就是它们都可以驱动BUFG和BUFH,这就意味着,从MRCC和SRCC进来的时钟都可以access全局时钟树,也就都可以当做全局时钟。所以,SRCC进来的时钟,虽然不能直接驱动其他clock region,但接到BUFG上之后,仍然可以通过BUFG来驱动其他的clock region。

其中有一点很关键,就是它们都可以驱动BUFG和BUFH,这就意味着,从MRCC和SRCC进来的时钟都可以access全局时钟树,也就都可以当做全局时钟。所以,SRCC进来的时钟,虽然不能直接驱动其他clock region,但接到BUFG上之后,仍然可以通过BUFG来驱动其他的clock region。

2023.8.21

1,晶振输出波形有正弦波和方波两种。晶体谐振器(无源晶振)输出波形为正弦波,晶体振荡器(有源晶振)输出波形为方波。其实有源晶振本身输出也是正弦波,但是当它内部增加了整形电路后,其输出就变成了方波。方波是数字电路中最常用的输出类型。

2,无源晶振:无源晶振是有2个引脚的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来。无源晶振信号质量较差,通常需要精确匹配外围电路(用于信号匹配的电容、电感、电阻等),更换不同频率的晶体时周边配置电路也需要做相应的调整。

有源晶振:有源晶振有4个引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件,因此体积较大,只需要电源,就可输出比较好的波形。有源晶振的封装通常有4个引脚,分别为VCC(电压)、GND(地)、OUT(时钟信号输出)、NC(空脚)。

有源晶振不需要CPU的内部振荡器,信号稳定,质量较好,而且连接方式比较简单(主要做好电源滤波,通常使用一个电容和电感构成滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路,如下:

2023.8.22

1,EMC(Electro Magnetic Compatibility,电磁兼容)是指电子、电气设备或系统在预期的电磁环境中,按设计要求正常工作的能力。它是电子、电气设备或系统的一种重要的技术性能,其包括三方面的含义:

(1)EMI(Electro Magnetic Interference,电磁干扰):

即处在一定环境中的设备或系统,在正常运行时,不应产生超过相应标准所要求的电磁能量,相对应的测试项目根据产品类型及标准不同而不同,对于民用、工科医、铁路产品,基本的EMI测试项目有:

● 电源线传导骚扰(CE)测试;

● 信号、控制线传导骚扰(CE)测试;

● 辐射骚扰(RE)测试;

● 谐波电流(Harmonic)测量;

● 电压波动和闪烁(Fluctuation and Flicker)测量。

对于军用产品,基本的EMI测试项目有:

● CE101测试:15 Hz~10 kHz电源线传导发射测试;

● CE102测试:10 kHz~10 MHz电源线传导发射测试;

● CE106测试:10 kHz~40 GHz天线端子传发发射测试;

● CE107测试:电源线尖峰信号(时域)传导发射测试;

● RE101测试:25 Hz~100 kHz磁场辐射发射测试;

● RE102测试:10 kHz~18 GHz电场辐射发射测试;

● RE103测试:10 kHz~40 GHz天线谐波和乱真输出辐射发射测试;

对于汽车及车载电子、电气产品,基本的EMI测试项目有:

● 汽车整车辐射发射测试;

● 车载电子、电气零部件/模块的传导骚扰测试;

● 车载电子、电气零部件/模块的辐射发射测试;

● 车载电子、电气零部件/模块的瞬态发射骚扰测试;

注:传导骚扰即为传导发射;辐射骚扰 即为辐射发射。

(2)EMS(Electro Magnetic Susceptibility,电磁抗扰度):

即处在一定环境中设备或系统,在正常运行时,设备或系统能承受相应标准规定范围内的电磁能量干扰,相对应的测试项目也根据产品类型及标准不同而不同,对于民用、工科医、铁路产品,基本的EMS测试项目有:

● 静电放电抗扰度(ESD);

● 电快速瞬变脉冲群抗扰度(EFT);

● 浪涌(SURGE);

● 辐射抗扰度(RS);

● 传导抗扰度(CS);

● 电压跌落与中断(DIP)。

对于军用产品,基本的EMS测试项目有:

● CS101测试:25 Hz~50 kHz电源线传导敏感度测试;

● CS103测试:15 kHz~10 GHz天线端子互调传导敏感度测试;

● CS104测试:25 Hz~20 GHz天线端子无用信号抑制传导敏感度测试;

● CS105测试:25 Hz~20 GHz天线端子交调传导敏感度测试;

● CS106测试:电源尖峰信号传导敏感度测试;

● CS114测试:10 kHz~400 MHz壳体电流传导敏感度电缆束注入传导敏感度测试;

● CS115测试:电缆束注入脉冲激励传导敏感度测试;

● CS116测试:10 kHz~100 MHz电缆和电源线阻尼正弦瞬变传导敏感度测试;

● RS101测试:25 Hz~100 kHz磁场辐射敏感度测试;

● RS103测试:10 kHz~40 GHz电场辐射敏感度测试;

● RS105测试:瞬变电磁场辐射敏感度测试。

对于汽车及车载电子、电气零部件产品,基本的EMS测试项目有:

● 符合ISO7637-1/2标准规定的电源线传导耦合/瞬态抗扰度测试;

● 符合ISO7637-3标准规定的传感器电缆与控制电缆传导耦合/瞬态抗扰度测试;

● 符合ISO11452-7(对应国标为GB17619)标准规定的射频传导抗扰度测试;

● 符合ISO11452-2(对应国标为GB17619)标准规定的辐射场抗扰度测试);

● 符合ISO11452-3(对应国标为GB17619)标准规定的横电磁波(TEM)小室的辐射场抗扰度测试);

● 符合ISO11452-4(对应国标为GB17619)标准规定的大电流注入(BCI)抗扰度测试);

● 符合ISO11452-5(对应国标为GB17619)标准规定的带状线抗扰度测试;

● 符合ISO11452-6(对应国标为GB17619)标准规定的三平板抗扰度测试;● 符合ISO10605标准的静电放电抗扰度测试。

(3)电磁环境:即系统或设备的工作环境。

2023.9.11

最近画的板子,有一个以太网的需求,所以就对以太网进行了部分学习。MCU芯片选用型号为STM32F429ZGT6。

1,以太网外设(ETH)

STM32F42x系列控制器内部集成了一个以太网外设,它实际是一个通过DMA控制器进行介质访问控制(MAC),它的功能就是实现MAC层的任务。借助以太网外设,STM32F42x控制器可以通过ETH外设按照IEEE 802.3-2002标准发送和接收MAC数据包。ETH内部自带专用的DMA控制器用于MAC,ETH支持两个工业标准接口介质独立接口(MII)和简化介质独立接口(RMII)用于与外部PHY芯片连接。MII和RMII接口用于MAC数据包传输,ETH还集成了站管理接口(SMI)接口专门用于与外部PHY通信,用于访问PHY芯片寄存器。

具体的MII,RMII的解释,请参考这篇博客:https://blog.csdn.net/qq_37659014/article/details/123664699?spm=1001.2014.3001.5506

2,我们这所用的网线为4线制,对外接口采用的型号为RJ45

3, ADC的参考电压:

这个参考电压也叫做基准电压,如果没有基准电压,就无法确定被测信号的准确幅值。例如基准电压为2.5V,则当被测信号达到2.5V时ADC输出满量程读数,使用者就会知道ADC输出的满量程等于2.5V。不同的ADC,有的是外接基准,也有的是内置基准无需外接,还有的ADC外接基准和内置基准都可以用,但外接基准优先于内置基准。

假如你选择的参考电压是5v,你的ad是12位的,那么当你的输入电压是5v的时候你的单片机的显示应该是4096(2^12=4096),如果是0v的输入那单片机里面的值就是0 ,中间点的值成线性关系,就是说假如你的输入是m,那单片机单片机的值就是4096*m/5,这样反过来你知道了单片机的值就可以算出你的输入是多少了!

【注1】还有在信号地和模拟地之间加上一个电感是为了去干扰,就像在VCC和GND之间用电容一样。

【注2】ad转换时的参考电压是内部T行网络的标准电压,参考电压可以认为是你的最高上限电压(不超过电源电压),当信号电压较低时,可以降低参考电压来提高分辨率。改变参考电压后,同样二进制表示的电压值就会不一样,最大的二进制(全1)表示的就是你的参考电压,在计算实际电压时,就需要将参考电压考虑进去。参考电压的稳定性对你的系统性能有很大的影响。

2023.9.12

模拟地和数字地之间的连接方法

1、 模拟地和数字地单点接地

只要是地,最终都要接到一起,然后入大地。如果不接在一起就是"浮地",存在压差,容易积累电荷,造成静电。地是参考0电位,所有电压都是参考地得出的,地的标准要一致,故各种地应短接在一起。人们认为大地能够吸收所有电荷,始终维持稳定,是最终的地参考点。虽然有些板子没有接大地,但发电厂是接大地的,板子上的电源最终还是会返回发电厂入地。如果把模拟地和数字地大面积直接相连,会导致互相干扰。不短接又不妥,理由如上有四种方法解决此问题:

a、用磁珠连接;

b、用电容连接;

c、用电感连接;

d、用0欧姆电阻连接。

磁珠的等效电路相当于带阻限波器,只对某个频点的噪声有显著抑制作用,使用时需要预先估计噪点频率,以便选用适当型号。对于频率不确定或无法预知的情况,磁珠不合。

电容隔直通交,造成浮地。

电感体积大,杂散参数多,不稳定。

0欧电阻相当于很窄的电流通路,能够有效地限制环路电流,使噪声得到抑制。电阻在所有频带上都有衰减作用(0欧电阻也有阻抗),这点比磁珠强。

2、跨接时用于电流回路

当分割电地平面后,造成信号最短回流路径断裂,此时,信号回路不得不绕道,形成很大的环路面积,电场和磁场的影响就变强了,容易干扰/被干扰。在分割区上跨接0欧电阻,可以提供较短的回流路径,减小干扰。

3、配置电路

一般,产品上不要出现跳线和拨码开关。有时用户会乱动设置,易引起误会,为了减少维护费用,应用0欧电阻代替跳线等焊在板子上。空置跳线在高频时相当于天线,用贴片电阻效果好。

4、其他用途

布线时跨线调试/测试用:在开始设计时,要串一个电阻用来调试,但是不不能确定具体的值,加了这么一个器件后方便以后电路的调试,如果调试的结果不需要加电阻,就加一个0欧姆的电阻。临时取代其他贴片器件作为温度补偿器件 更多时候是出于EMC对策的需要。另外,0欧姆电阻比过孔的寄生电感小,而且过孔还会影响地平面(因为要挖孔)。

因为项目中经常用到磁珠,且上面说了磁珠也需要选型,对应频点,故去学习了一下磁珠的作用。

磁珠的参数、选型、直流重叠特性

1, 对磁珠的认识:

磁珠是一种电感型EMI静噪滤波器,实物和电感很像,现在用的最多的是铁氧体磁珠(Ferrite Bead)。磁珠的单位是欧姆,根据型号的不同,可以抑制几MHz~几GHz的噪声,经常被用在信号线和电源线上(串联使用)。

磁珠和电容、电感滤除噪声有很大不同,电容主要提供一个地阻抗路径(隔直通交),电感是将噪声反射出去(隔交通直),磁珠如何滤除噪声在下面会提及。

2, 磁珠和电感的相同点和不同点:

磁珠和电感的在电路中的符号是一样的,却是不一样的器件,磁珠单位是欧姆(Ω),电感单位是亨(H)。

磁珠由氧磁体组成,电感由磁芯和线圈组成,磁珠把交流信号转化为热能,电感把交流存储起来,缓慢的释放出去,所以说电感是储能,而磁珠是能量转换(消耗)器件。

我们都知道EMI有两个途径,辐射和传导,磁珠和电感都可以解决EMC和EMI问题,但是侧重点不同。

磁珠主要解决辐射干扰问题,信号线上多用磁珠,某一些高频电路如RF、振荡电路、DDR SDRAM等都需要在电源输入部分加磁珠。

电感主要解决传导干扰问题,高频电感主要用于中低频滤波电路、RF匹配等,功率电感主要用于DC-DC电路中。

3, 磁珠的主要参数:

① 阻抗|Z|:业界习惯,磁珠的阻抗由100MHz时的阻抗确定,所以我们经常在磁珠的SPEC里看到100R@100MHz,指的是在100MHz频率下,磁珠的阻抗是100R,阻抗越大,抑制噪声的效果越好,有一些高频磁珠给出的阻抗是在1GHz频率下。

有一点需要注意,看上图,在100MHz时,磁珠的阻抗并不是最大的,所以在选型时可以根据噪声频点,选择频点附近阻抗最大的型号。

100MHz在某种意义上只是一个标准,仅仅只是一个标准,个人觉得并没有太大的实际意义,因为磁珠在实际的应用中,随着频率的改变,阻抗会相应的发生变化。所以说,单点接地用磁珠的情况很少,需要提前评估噪声的频率范围。

② 直流电阻DCR:指直流电流通过磁珠时,磁珠呈现的电阻值,DCR一般越小越好,对有用信号的衰减越小。

③ 额定电流Rated Current:指磁珠正常工作时允许的最大电流。

4, 磁珠的直流重叠特性

我们都知道在电容上加不同的直流电压,电容容量是会变化的。磁珠也有同样的直流重叠特性,片状铁氧体磁珠是一种使用铁氧体的电感器。因此,当大电流通过时,需要特别注意由于磁饱和所造成的性能改变。

从上图可以看出,通过磁珠的电流增大时,其阻抗会下降,阻抗下降就意味着抑制噪声的性能会变差,电流减小时,阻抗又会变大,性能会复原。

所以在选型时,我们要考虑好额定电流和阻抗这两个参数。

5, 磁珠的等效模型

磁珠的等效模型可以简化为一个电感和一个电阻串联,当然还会有DCR和寄生电容参数,在这里不作说明。

电感和电阻都是频率的函数,所以磁珠的阻抗为Z=R+JWL,下图所示,箭头处对应的频率称之为交叉频率,有的叫转折频率。

小于交叉频率,Z和XL几乎是重合的,此时的磁珠呈感性,小电感,此时反射噪声;大于交叉频率时,Z和R曲线几乎是重合的,此时磁珠呈电阻特性,大电阻,起吸收噪声并转变为热能的作用。

交叉频率越大,磁珠呈现感性的频段越宽,对低频的吸收能力越弱,对高频的吸收能力越强。交叉频率越小,磁珠呈现感性的频段越窄,对低频的吸收能力越强,对高频的吸收能力越弱。

6, 磁珠选型注意事项

a) 分析有用信号和噪声的频率:噪声的频段要大于交叉频率,便于磁珠吸收噪声而不是反射噪声;信号的频率小于交叉频率,防止信号被衰减。

b) 考虑DCR的大小:直流电路中,防止DCR过大,导致信号衰减,比如5V 500mA的电源,经过一个DCR=1R的磁珠时,电压会衰减500mA*1R=0.5V。 一般情况下,交流阻抗越大,滤除噪声好,但是DCR也会大,对有用信号有衰减,所以这是一个权衡的过程。

c) 考虑额定电流的大小:不要为了省成本,而一味选择低额定电流的磁珠,考虑到直流重叠特性,随着电流的变大,阻抗下降,吸收噪声性能也会下降。 举个例子,某电路大部分时间工作电流为300mA以下,最高会到400mA,但是很少,此时可以选择额定电流为400mA的磁珠。

2023.9.13

以太网网络变压器设计

1, 为什么要加入网络变压器?

从理论上来说,是可以不需要接变压器,直接接到RJ45上,也许能正常工作的。但是传输距离就很受限制,而且当接到不同电平网口时,也会有影响。而且外部对芯片的干扰也很大。当接了网络变压器后,它主要用于信号电平耦合。其一,可以增强信号,使其传输距离更远,其二,使芯片端与外部隔离,抗干扰能力大大增强,而目对芯片增加了很大的保护作用(如雷击),其三,当接到不同电平(如有的PHY芯片是2.5V,有的PHY芯片是3,.3V) 的网口时,不会对彼此设备造成影响。至于掏空的原因是为了防止变压器转换的时候影响下面的电源和地(变压器的下方尽量不要接地和电源)。

2, 参考设计(中间抽头的接法)

这个主要是与使用的PHY芯片UTP口驱动类型决定的,这种驱动类型有两种,电压驱动和电流驱动。电流驱动的就要接电源;电压驱动的就直接接个电容到地即可!所以对于不同的芯片,中心抽头的接法,与PHY是有密切关系的,具体还要参看芯片的datasheet和参考设计了。为什么接电源时,又接不同的电压呢?这个也是所使用的PHY芯片资料里规定的UTP端口电平决定的。决定的什么电平,就得接相应的电压了。即如果是2.5v的就上拉到2.5v,如果是3.3v的就上拉到3.3v。

如果网络变压器的中心抽头需要提供一个VCC (3.3V、2.5V等等,下同)电源的就是电流驱动:

我所使用的以太网芯片型号为:DP83848,属于电流驱动,故中间抽头也需要上拉。

主要参考这一篇博客:

以太网介绍及硬件设计文章来源:https://www.toymoban.com/news/detail-738744.html

好了,完成任务,以上便是这段时间拖更的一些内容,希望大家一起学习进步,很多都是自己学习过程中遇到的一些疑问,以后的文章,我就尽量标明博客参考路径,这样的话大家能够更全面的学习,只看我的记录有点片面,可能大家的侧重点并不一致,大家遇到问题一定要学会自己去搜索!

后续会持续更新,若有错误,还望指正!文章来源地址https://www.toymoban.com/news/detail-738744.html

到了这里,关于【硬件学习之路】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!