FPGA学习笔记:verilog基础代码与modelsim仿真(三)

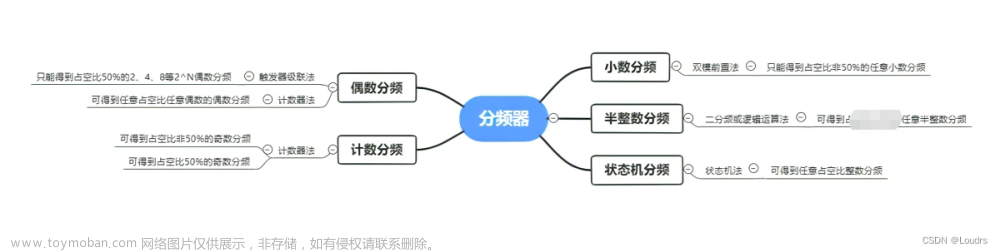

1. 分频器——偶分频

方法1:

verilog代码实现:

module divider_six(

input wire sys_clk ,

input wire sys_rst_n ,

output reg clk_out

);

reg [1:0] cnt ; //00 01 10

wire [1:0] max_cnt = 2'd2;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 2'b0;

else if(cnt == max_cnt)

cnt <= 2'b0;

else

cnt <= 2'd1 + cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_out <= 1'b0;

else if(cnt == max_cnt)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule

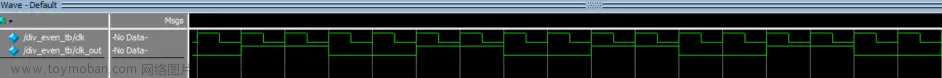

modelsim仿真波形图:

方法2(推荐):

比起方法一直接使用计数器定义一个新的时钟波形,方法二使用flag_out作为分频变量从而实现分频器的功能。虽然二者都使用了计数器,但方法二显然更符合“分频”的定义,且此方法在告诉电路中更加稳定,所以在实际分频应用中更推荐这种方法。

verilog代码实现:

module divider_six(

input wire sys_clk ,

input wire sys_rst_n ,

output reg flag_out

);

reg [2:0] cnt ; //00 01 10

wire [2:0] max_cnt = 3'd5;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 3'b0;

else if(cnt == max_cnt)

cnt <= 3'b0;

else

cnt <= 3'd1 + cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

flag_out <= 1'b0;

else if(cnt == max_cnt -3'd1)

flag_out <= 1'b1;

else

flag_out <= 1'b0;

endmodule

仿真代码:

`timescale 1ns/1ns

module tb_divider_six();

reg sys_clk;

reg sys_rst_n;

wire flag_out;

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk; //clk frequency

divider_six divider_six_inst

(

.sys_clk (sys_clk) ,

.sys_rst_n(sys_rst_n) ,

.flag_out (flag_out)

);

endmodule

modelsim仿真波形:

2. 按键消抖

verilog代码实现:

module key_filter

#(

parameter CNT_MAX = 20'd999_999

)

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire key_in ,

output reg key_flag

);

reg[19:0] cnt_20ms ;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_20ms <= 20'd0;

else if(key_in == 1'b1)

cnt_20ms <= 20'd0;

else if(cnt_20ms == CNT_MAX)

cnt_20ms <= cnt_20ms;

else

cnt_20ms <= cnt_20ms + 20'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

key_flag <= 1'b0;

else if(cnt_20ms == CNT_MAX - 1'd1)

key_flag <= 1'd1;

else

key_flag <= 1'd0;

endmodule

仿真代码:

`timescale 1ns/1ns

module tb_key_filter();

reg sys_clk;

reg sys_rst_n;

reg key_in;

reg[7:0] tb_cnt;

wire key_flag;

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk; //clk frequency

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

tb_cnt <= 8'd0;

else if (tb_cnt == 8'd249)

tb_cnt <= 8'd0;

else

tb_cnt <= tb_cnt + 8'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

key_in <= 1'b1;

else if(((tb_cnt >= 8'd19) && (tb_cnt <= 8'd69))

|| ((tb_cnt >= 8'd149) &&(tb_cnt <= 8'd169)))

key_in <= {$random} % 2 ;

else if (tb_cnt >= 8'd69 && tb_cnt <= 8'd149)

key_in <= 1'b0;

else

key_in <= 1'b1;

key_filter

#(

.CNT_MAX(20'd24)

)

key_filter_inst

(

.sys_clk (sys_clk) ,

.sys_rst_n(sys_rst_n) ,

.key_in(key_in) ,

.key_flag (key_flag)

);

endmodule

文章来源:https://www.toymoban.com/news/detail-739192.html

modelsim仿真波形:

文章来源地址https://www.toymoban.com/news/detail-739192.html

文章来源地址https://www.toymoban.com/news/detail-739192.html

到了这里,关于FPGA学习笔记:verilog基础代码与modelsim仿真(三)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!