传输层的主要功能是根据用户配置的链路参数,对转换器得到的原始样本数据进行映射,从而产生宽度为8bit 的特定格式数据,并视实际应用情景添加控制位或者尾位,以满足格式需求。

【JESD204系列】五、传输层设计原理1. 概述

在JESD204B 协议所规定的链路参数中,主要通过L 决定链路通道数,S 决定采样倍数,因此数据映射方式根据链路的通道数量L 分为单通道链路和多通道路两种,又可以根据S 的取值分为正常采样和过采样两种。用户在使用中,通过配置链路参数来决定数据的映射方式。

JESD204B 对于如何映射提供了以下几个可选的配置:

a.一个转换器到一个单通道链路;

b.同一个设备的多个转换器到一个单通道链路;

c.一个转换器到一个多通道链路;

d.同一个设备的多个转换器到一个多通道链路。

单个转换器可以映射到单通道链路或多通道链路,这种配置对于ADC 的宽带RF应用非常有利,配置模式的选取由ADC 的采样速率决定。对于第三种映射关系,一些应用中,单个转换器有时需要多个通道,具体要看对应ADC 的通道速率的最大值。

链路配置参数含义及取值范围:

| 参数名 | 含义 | 取值范围 |

|---|---|---|

| M | 每个设备中的转换器数 | 1-256 |

| L | 每个转换器链路的通道数 | 1-32 |

| F | 每个帧中的字节数 | 1-256 |

| S | 每帧中每个转换器的采样点数,通常情况每一帧传输1个采样数据 | 1-32 |

| N | 转换器分辨 | 1-32 |

| N’ | 每个采样的总比特数 | 1-32 |

| K | 每个多帧中帧的数量 | 1-32 |

| CF | 每个链路每个帧周期的控制字数量 | 0-32 |

| CS | 每个采样的控制比特数 | 0-3 |

| HD | 高数据密度模式使能,HD=1时样本分到1个以上的通道中 | 0-1 |

在传输层,一组样本或部分样本被分组成F个八位字节的帧。“帧”数据结构是指一组连续的八位字节(8b/10b 编码器的输出都是一个八位字节),其中每个八位字节的位置都以帧对齐信号作为参考。“多帧”数据结构是指一组连续的帧,其中每个多帧的位置都以多帧对齐信号作为参考。 在许多应用中,帧时钟将具有与采样时钟相同的频率。JESD204 协议允许在每个帧周期内每个转换器传输多个采样,S 必须总是整数,这样可以最小化SERDES 电路和敏感模拟部件之间的串扰。每个采样作为一组N’比特发送,由N个数据比特,CS位的可选控制位和T位的可选尾位组成,在帧的结尾处的附加尾比特是必需的,这样可以在每个帧周期中填充每个通道使比特总数为整数个八位字节。

基本公式:

每个采样的总比特数: N’=(N + CS + T)

JESD204数据速率 =(M X ADC样本速率)/ADC抽取系数

每一帧传输的采样数: S=(JESD204 数据速率)/帧时钟速率(FC)

通道线路速率: Lanerate=(M×S×N′×10/8×FC)/L

每一帧的字节数(octets): F=(M×S×N′)/(8×L)

2. 单通道数据映射

本节主要分析在单个链路中对来自同一设备中的一个或多个转换器的采样到八位字节的映射。JESD204B 兼容了JESD204A,但是尾位的位置可能不同于2006年4月的JESD204版本。

2.1 不采用过采样的用户数据映射

没有过采样的映射参考下图:一个器件包含M 个转换器,每个转换器每个采样产生N 个数据位。图片中所有的编号都是从0 开始。在一个样本内,最左边的位是最高有效位(MSB),最右边的位是最低有效位(LSB)。

主要是通过以下几个步骤将样本数据映射成8bit 数据: 1字=2字节(1 word = 2 byte),1字节=8位(1 byte = 8bit)

1.样本数据以线性方式进行映射,按照转换单元顺序从0开始直至所有样本数据都被映射完成。

2.样本被映射到字。

当样本不包含控制位时,字(16bit)就等于样本数据,当采样器有有效的控制位时,映射就分为以下两种情况:

- a 每次采样数据的控制位对应在转换样本的最低位。

- b 控制位单独映射成一个字(16bit),采样数据映射成转换字,控制字的第一个bit 对应转换单元0的控制字,控制字的第二个bit 对应转换单元1的控制字,以此类推。

对于独立的通道CF=0或CF=1,每一帧周期总的字个数就是M+CF。

3.包含的bit 数不是4的倍数,在构成最小的nibble group 时会使用tail bits。在图中被称为“NG”,如果系统对传输效率要求很高时这一步骤是可以跳过的,当N′>N 时,N′是4的倍数,并且大于部分的值由congtrol bit 和tail bit 填充。

当CF=0时,control bit 被当作data word 的一部分,在control bit 和data bit 之间没有tail bits,但在control bits 后面会有一个或者更多的tail bits。当CF=1时,样本数据和控制字在不同的字里面,每一样本数据字后的一个或者更多的tail bits 也是必须的。

4.Tail bits 必须保证在数据映射完成后,数据帧的bit 数是8的倍数也就是帧数个字节。

5.上述步骤映射形成的帧将被分解成F个八位字,传输到数据链路层。

尾比特位推荐位置

图2表示了2006年的JESD204 及更高版本的Tail bits的推荐位置的差异。在版本2006中,Tail bits仅在帧的末尾插入。如果需要填充一个半字节组,较新的版本建议在每个样本的末尾插入Tail bits。在该示例中,新的映射方法每帧需要一个额外的八位字节。

使用控制字压缩帧结构

图3表示出了如何将控制位分组为控制字以便减少尾位的数量并且使帧更短。

2.2 过采样下的用户数据映射

过采样状态,即每帧每个转换器所发送的样本数量为1个以上。其映射方式与正常数据映射方式是相似的,映射的原则如下图4所示。但需注意的是,在映射下一个转换器的数据之前,每个转换器的 S个样本都是级联的而不是每个转换器一个样本 。 下图5所示,是过采样状态下的数据映射,以 4个12位转换器采样数据的映射为例。其中每个转换器在每个帧周期中采集两个 12位的样本数据, Cr0 S0表示序号为 0的转换器采到的第一个数据样本,其它的以此类推。这是一个两倍过采样下加一个控制字的数据映射。

下图5所示,是过采样状态下的数据映射,以 4个12位转换器采样数据的映射为例。其中每个转换器在每个帧周期中采集两个 12位的样本数据, Cr0 S0表示序号为 0的转换器采到的第一个数据样本,其它的以此类推。这是一个两倍过采样下加一个控制字的数据映射。

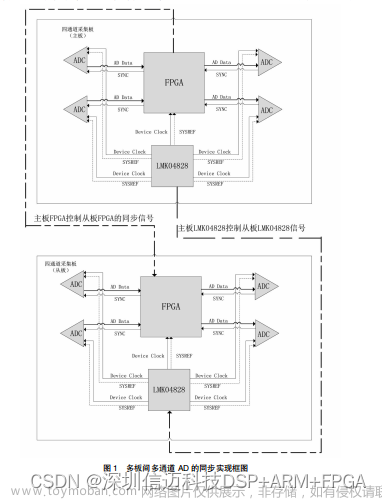

3. 多数据通道的数据映射

对于一个通道数为L 的多通道链路来说,数据映射的方式基本与单通道数据映射相同。唯一的区别是最后一步,将数据排列为L×F的一排,然后前F个8bit字节通过通道0传输,下F个8bit 字节通过通道1传输,以此类推,最后F个8bit字节由通道L−1传输。

除了基本的数据映射规则之外,在进行多通道的数据映射时还须遵守一些额外的规则:

- 参数HD 决定是否工作在高分辨率模式下。当HD=0,即低分辨率模式下,通过在组最后一个完整的4位半字节组( NG)之后添加更多的尾位 T,避免在一组 F个八位字节的末端出现不完整的转换字。在HD=1 的高分辨率模式下,一个处理后的字可以被分割到不同的通道。

- 参数CF 代表了每个链路每个帧周期控制字的总数,以及在多通道传输的数据映射时,决定了哪一些通道传输控制字。当CF=0 时,代表不添加控制字。当CF≠0 时,CF 的取值必须为参数M和参数L的公因数。代表着将L条通道分成CF组,其中每一组包含𝐿/𝐶𝐹条通道,分别传输𝑀/𝐶𝐹个转换单元的数据。在这些采样之后,插入控制字,连续插入是为了控制比特属于这些采样。如果控制字在单个线路上传输,则不允许在线路边界上分开控制字。

示例:带有和不带控制字的16×(11 + 2)位转换器的映射

下图7显示了一个16×11位转换器的映射,每个采样有两个控制位,不使用控制字。附加的控制位将每个11比特的采样扩展到13比特,其通过增加尾部位进一步扩展到四比特的半字节。一共有32个八位字节,他们必须在一个帧周期期间发送,可以使用8条线路每帧4 字节的传输方法。

下图8表示了将所有控制比特组成一个控制字放在最后一条lane 上传输,这样便将每个帧周期发送的八位字节的总量减少到28 个。这样可以节省一个线路。上述映射方式的优点在于只需要七个通道传输数据,但缺点是在只有某些特定的转换器单元工作时,不能像前文图7的打包方式那样,只激活特定的几个通道进行工作即可进行传输,从而起到降低功耗的效果。由于HD=1,一个转换器单元得到的采样点可能需要多个通道进行传输。比如只有仅发送转换器2 数据,在图7的映射中激活线路1就足够了,而线路0,1 和6 必须在图8的映射中有效。

图9显示了在同一个转换器中使用两个控制字的映射。

在上图中,有两个控制字,即可以划分为两组数据,根据L/CF=4 确定每组有4个lane,包含M/CF=8 个数据采样和16 个控制比特。文章来源:https://www.toymoban.com/news/detail-739969.html

在进行数据映射时,可以根据使用需求,将控制位设置为0或1,从而实现控制功能。尾位则可以配置为任意数据,因为尾位的作用只是用来补充数据到特定的位数,并没有实际意义。并且在数据映射时,尾位和控制位可以单独使用或同时使用,也可以都不使用。文章来源地址https://www.toymoban.com/news/detail-739969.html

到了这里,关于【JESD204系列】五、传输层设计原理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!