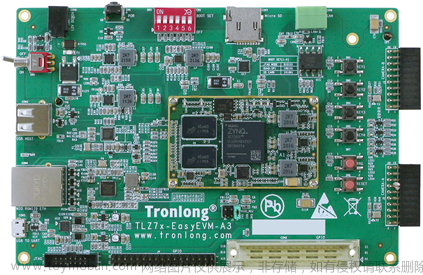

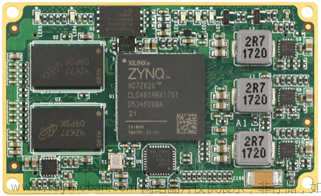

【ALINX】FPGA ZYNQ视频教程——AX7010/AX7020教程——FPGA实验篇

02_Vivoda初体验LED灯工程

2.1 新建Vivado工程

- File=>New Project

- 工程文件命名:不能出现中文、空格等非法字符

- 选择芯片型号:

视频定位链接 03:45

- AX7020开发板速度选择“-2”;型号选择“xc7Z020clg400-2”

** Vivado窗口介绍

视频定位链接05:44

2.2 添加源文件

视频定位链接 08:43

1.选择点击:窗口Source,左上角“+”;选择“Add ~ design sources”

2.选择“create file” 或直接选择目录下的源文件

3.定义模块:将模块名称设计和文件名一样

2.3 编辑Design Sources源文件(.v)

视频定位链接 10:21

1.选择点击:窗口Source–》Design Sources–》XXX.v模板 源文件

2.编辑源文件时,编辑框的右上角方块如果为绿色,则表示程序无误,若为红色则表示异常,可通过中间红色小块进行查找。

//led.v文件代码

module led(

input sys_clk,

input rst_n,

(* MARK_DEBUG="true" *)output reg [3:0] led

);

(* MARK_DEBUG="true" *)reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge rst_n)

begin

if (!rst_n)

begin

led <= 4'd0 ;

timer_cnt <= 32'd0 ;

end

else if(timer_cnt >= 32'd49_999_999)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

Instantiate ila in source file

//ila ila_inst(

// .clk(sys_clk),

// .probe0(timer_cnt),

// .probe1(led)

// );

endmodule

2.4 RTL ANALYSIS (RTL分析)

视频定位链接 12:49

1.选择点击:左侧 RTL ANALYSIS => Open Elaborated Design

2.进行引脚绑定,将FPGA的输入和输出设备绑定到FPGA的引脚上

1)切换到右下角"I/O Ports"窗口,可从标题栏 Window 中调出。

2)根据原理图或者用户手册,将外设与FPGA进行引脚绑定和电平匹配,在"Package Pin" 输入引脚号,在"I/O Std"处选择FPGA的Bank(3.3V时选择LVCMOSE33)

3)保存后,约束文件类型为==.XDC==

4)在Sources窗口的Constraints目录下会出现.XDC约束文件

3.SYNTHESIS (综合)

1).选择点击:左侧 SYNTHESIS => Run Synthesis 选择核心数;开始综合,右上角有指示。

2)时序约束

视频定位链接 21:29

- 选择点击:左侧 SYNTHESIS => Open Synthesized Design =>Constranints Wizard

- 设置时钟频率(50MHZ),“Skip to Finish”

3).在Sources窗口的Constraints的.xdc约束文件中点击“reload”,补充时序约束。

2.5 编译:生成Bit文件

视频定位链接 23:32

1.选择点击:左侧 PROGRAM AND DEBUG => GENERATE bITSTREAM

2.选择运行处理器核心数(越多电脑越卡);右上角会显示运行状态。

2.6 仿真

视频定位链接 25:27

1.右键选择点击:左侧 SIMULATION => Simulation Settings

2.设置:仿真器、仿真语言、初始仿真时间(50ms)等参数.

3.添加仿真源文件

1).选择点击:窗口Source,左上角“+”;选择“Add ~ simulation sources”;设置文件名:vtf_led_test

2).在该目录下编辑仿真源文件(编程)

`timescale 1ns / 1ps

//

// Module Name: vtf_led_test

//

module vtf_led_test;

// Inputs

reg sys_clk;

reg rst_n ;

// Outputs

wire [3:0] led;

// Instantiate the Unit Under Test (UUT)

led uut (

.sys_clk(sys_clk),

.rst_n(rst_n),

.led(led)

);

initial

begin

// Initialize Inputs

sys_clk = 0;

rst_n = 0 ;

#1000 ;

rst_n = 1;

end

//Create clock

always #10 sys_clk = ~ sys_clk;

endmodule

4.运行(行为级)仿真:选择点击 SIMULATION => Run Simulation => Run Behaviorral Simulation

5.仿真操作:

视频定位链接 29:59

1)选择 Scope(模块) => Objects(项目);左键按住则可以拖动到黑色仿真窗口。

2)Restart(重新运行)、Run All(一直运行)、Run for

xx(仿真运行xx长时间)

3)仿真文件存储目录(.sim文件夹)

4)显示进制选择:黑框仿真栏项目,鼠标右键 => Radix => Unsigned Decimal(十进制)

2.7 程序下载

视频定位链接 34:40

1.硬件连接:电源线、JTAG下载口(跳线帽也换到JTAG)

2.选择点击:左侧 PROGRAM AND DEBUG => Open Hardware Manager;在左上角通知栏点击“++Open Target++” => Auto Connect

3.右键选择点击:Hardware中XC7z020_1 => Program Device;选择2.5中生成的.Bit文件

2.8 内嵌逻辑分析仪(可获取开发板的真实数据)的用法

2.8.1 利用IP进行例化

视频定位链接 36:32

1.选择点击:左侧 PROJECT MANAGER => IP Catalog

2.在搜索栏中搜索ILA(Integrated Logic Analyzer);双击进入

3.设置参数

1)修改顶端文件名,设置 Number of Probe(探针数目)、Sample DataDepth(采样深度)。

2)设置 Probe Width(探针宽度):计数器是32位,4个led灯是4位。

4.保持默认,点击生成ILA文件(.xci)。

1)在Sources处点击打开ila文件,展开层级关系;

2)展开后,会生成ILA的.v文件

5.例化:

视频定位链接 40:50

1)复制ILA文件中的模块名及代码,在led.v文件内做 例化:将时钟(.clk)和探针(.probe)与需要探测的接口进行对应。

// 模块名为(ila)ILA中例化前代码:

ila (

clk,

probe0,

probe1

);

// led.v中例化后代码:

//Instantiate ila in source file

ila ila_inst(

.clk(sys_clk),

.probe0(timer_cnt),

.probe1(led)

);

2)重新下载程序,生成.bit文件,下载文件到开发板;注意此时下载时会多一个.ltx文件(用于描述逻辑分析仪连接)

3)选择点击: Run trigger… 则可显示开发板内的实际数据。

4)制作触发器

视频定位链接 45:09

选择点击: Add Probe(增加探针)=> 选择探针;修改探针逻辑、进制、数值;

5)修改 Trigger Position in window 可以调整窗口的前后显示比例;每次修改需要点击 Run trigger…

2.8.2 利用调试信息进行ILA

视频定位链接 49:07

1.在.v文件中添加调试信息

1)选择点击:PROJECT MANAGER => Language Templates;搜索 mark,选择“mark debug”

2)在led.v文件中的led和cnt值定义的前面加上Mark语句,保存。

2.进行综合(SYNTHESIS)

1)选择点击:左侧 SYNTHESIS => Run Synthesis 选择核心数;开始综合,右上角有指示。

2)综合后,选择点击:SYNTHESIS => Open Synthesis => Set Up Debug;按照指示保持默认,生成后保存。

3)在约束文件处 reload ,约束文件中会将信号和探针连接到一起。

3.生成bit文件

4.下载调试(同上)文章来源:https://www.toymoban.com/news/detail-740297.html

《完》文章来源地址https://www.toymoban.com/news/detail-740297.html

到了这里,关于【ALINX】FPGA ZYNQ视频教程AX7020教程—02_Vivoda初体验LED灯工程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!