一.D触发器

1.原理

-

D触发器原理如下

-

D触发器模拟波形图如下

由图可知Q值不仅与D有关,同时需要考虑到clk上升沿到来后有效

2.代码

module DFF(

input clk,

input rst_n,

input d,

output q

);

reg q_r;

always @(posedge clk or negedge rst_n) begin

q_r <= d;

end

assign q = q_r;

endmodule

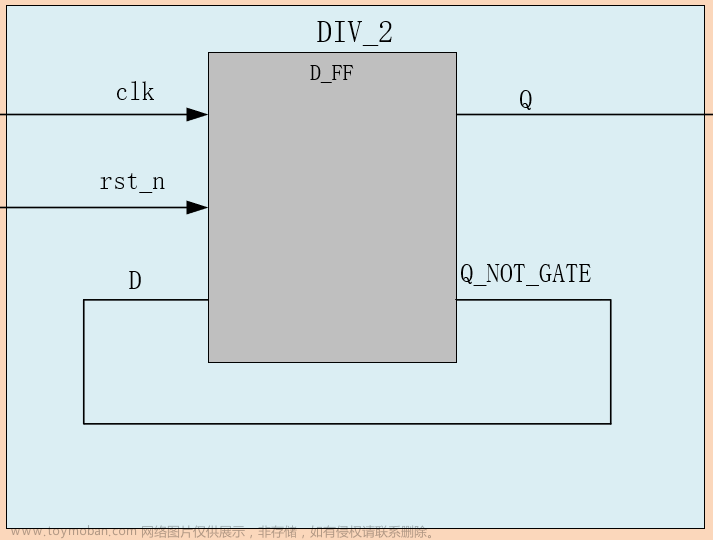

二.N分频器

1.原理

- 输入一个时钟信号,将输出的信号的时钟周期变为输入信号的时钟周期的N倍,我们将这种器件叫做N分频器。

2.实验任务

- 我们的目的是生成一个N分频器,可以实现任意比例分频。需要时仅需改变N的值即可实现不同的分频器。

3.设计思路

- 将clk上升沿下降沿都设为敏感信号,clk变化时计数。实现N分频器,计数器从0数到N-1,输出信号反转一次。注意:由于是从0开始计数,共计N个数,只需要计到N-1即可。

4.时序图

- 这里以5分频和8分频为例,分别探讨了奇数和偶数分频的情况。时序图是我们自己设想的效果,需要与我们的仿真效果比较。

5.代码

module N_divider #(parameter N = 5)(//N可以取我们需要的值,作为全局变量,它可以被更改

input clk,

input rst_n,

output reg clk_out

);

//计数,计N个数一清零

reg [N-1:0] cnt;

wire add_cnt;

wire end_cnt;

always @(clk) begin

if (!rst_n) begin

cnt <= 'd0;

end

else if (add_cnt) begin

if (end_cnt) begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 'd1;

end

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt == N - 1'd1;

//计满N个数clk_out反转一次

always @(clk) begin

if (!rst_n) begin

clk_out <= 'b1;

end

else if (cnt == N - 1'd1) begin//计满N个数反转

clk_out <= ~clk_out;

end

else begin//其余情况保持不变

clk_out <= clk_out;

end

end

endmodule

6.仿真文件

`timescale 1ns/1ns

module tb_N_divider #(parameter N = 5)();

reg tb_clk;

reg tb_rst_n;

wire tb_clk_out;

parameter CYCLE = 20;//周期

N_divider #(.N(N)) u_N_divider(

.clk (tb_clk),

.rst_n (tb_rst_n),

.clk_out(tb_clk_out)

);

initial tb_clk = 1'b1;

always #(CYCLE/2) tb_clk = ~tb_clk;//半个周期反转clk

initial begin

tb_clk = 1'b0;

tb_rst_n = 1'b0;

#20;

tb_rst_n = 1'b1;

#2000;

$stop;

end

endmodule

7.仿真效果

-

仍然以5分频和8分频为例,探究奇数和偶数的仿真效果

-

5分频波形图

文章来源:https://www.toymoban.com/news/detail-740435.html

文章来源:https://www.toymoban.com/news/detail-740435.html -

8分频波形图

文章来源地址https://www.toymoban.com/news/detail-740435.html

文章来源地址https://www.toymoban.com/news/detail-740435.html

到了这里,关于时序逻辑基础之D触发器&分频器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!