目录

2.0 DW_apb_i2c 版本

2.1 DW_apb_i2c 逻辑设计架构

2.2 DW_apb_i2c 特点

2.3 DW_apb_i2c 功能使用介绍

2.3.1 工作模式

2.3.2 开始信号

2.3.3 停止信号

2.3.4 从机地址模式

2.3.5 输入滤波功能

2.3.6 SCL速率配置

2.3.6.1 SCL 配置寄存器

2.3.6.2 SCL 计算公式

2.3.6.3 SCL 实例计算

2.3.7 总线清除功能

2.3.7.1 SDA 恢复

2.3.7.2 SCL 恢复

2.3.8 DMA功能

2.8.1 DMA 使能

2.8.2 DMA水线设置

2.3.9 SDA 保持时间

项目使用到Synopsys的DW_apb_i2c,本文作为个人学习心得和使用记录,仅作参考。

2.0 DW_apb_i2c 版本

目前我使用DW_apb_i2c协议是:DW_apb_i2c_2018,即2018版本。该版本支持下列标准协议:

(1)支持I2C总线标准6.0版本;

(2)支持SMBus规范3.0版本;

(3)支持PMBus规范1.2版本。

2.1 DW_apb_i2c 逻辑设计架构

DW_apb_i2c 逻辑设计结构图如下图1所示:

图1.I2C逻辑结构图

各个模块简单介绍如下:

- AMBA Bus Interface Unit:APB接口模块,接收APB接口信号并且转化成通用的接口信号。

- Register File:寄存器模块,同时也是软件访问接口。

- Slave State Machine:从设备状态机,实现slave功能,按照从设备协议,监控总线的地址,匹配地址,数据处理。

- Master State Machine:主设备状态机,实现master功能,产生i2c协议时序。

- Clock Generator:时钟产生模块,按照时序要求产生时钟信号、起始和停止信号,idle状态检查,数据建立和保持。

- Rx Shift:RX移位寄存器,接收SDA线上的串行数据,转化成并行数据保存在RX_FIFO中。

- Tx Shift:TX移位寄存器,处理TX_FIFO的数据,一位一位串行输出到i2c的SDA线上。

- Rx Filter:RX滤波器,检测总线上的事件,如开始事件、停止事件等。

- Toggle:生成脉冲并翻转,用于跨时钟域时传输信号。

- Synchronizer:同步时钟信号。

- DMA Interface:DMA交互接口。

- Interrupt Controller:中断控制器,产生并保存中断信号。

- RX FIFO:保存RX移位寄存器接收的数据。

- TX FIFO:接收并保存CPU从APB总线上传输的数据。

2.2 DW_apb_i2c 特点

下面对DW_apb_i2c的功能特点做一个简单概括:

- master/slave可配置,但是同一时刻,只能配置为其中一种模式;

-

支持4种速率模式:

- Standard mode (0 to 100 Kb/s)

- Fast mode (≤ 400 Kb/s)

- Fast mode plus (≤ 1000 Κb/s)

- High-speed mode (≤ 3.4 Mb/s)

- 支持7bit或者10bit地址模式;

- 支持DMA操作;

- 支持总线上的数据建立时间和保持时间可软件配置;

- 支持读写交替访问;

- 支持多主机共存时的时钟同步和总线仲裁;

- 支持PMBus;

- 支持Smbus,包括alert功能和2个从机地址功能等;

- 支持广播功能(general call);

- 支持总线清除功能,在数据线或者时钟线卡在低电平时,可以恢复正常;

- 支持超快模式(Ultra-Fast mode,5Mb/s)

2.3 DW_apb_i2c 功能使用介绍

2.3.1 工作模式

DW_apb_i2c 可以配置成master或者slave,支持下面4种工作模式

(1)Master模式发送数据:发送写请求,写数据到从设备;

(2)Master模式接收数据:发送读请求,接收来自从设备的数据;

(3)Slave模式发送数据:响应主设备的读请求,向主设备发送数据;

(4)Slave模式接收:响应写请求,接收来自主设备的数据;

2.3.2 开始信号

当DW_apb_i2c 作为 master 时,往TX FIFO中存入数据时(软件配置数据到寄存器IC_DATA_CMD[7:0]),DW_apb_i2c 会自动在总线上产生一个START信号,即START信号的产生不需要软件参与。

2.3.3 停止信号

停止信号的产生比较特殊,和TOP层参数 IC_EMPTYFIFO_HOLD_MASTER_EN 有关,这个参数在生成 DW_apb_i2c 逻辑代码的时候就选择好了,软件不可配置。

(1)当 IC_EMPTYFIFO_HOLD_MASTER_EN 配置为0

这种模式下,当发送FIFO为空时,DW_apb_i2c 会自动产生STOP信号,不需要软件参与。写和读的时序见下面 图2-11和 图2-12。

(2)当 IC_EMPTYFIFO_HOLD_MASTER_EN 配置为1

这种模式下,TX FIFO变为空后,需要往寄存器 IC_DATA_CMD[9] (stop位)中写入1,让 DW_apb_i2c 产生STOP信号;否则,DW_apb_i2c 不会产生 STOP信号 ,将保持SCL线为低电平来暂停传输。写和读的时序见下面 图2-14和 图2-15。

当 DW_apb_i2c 作为Slave时,不会产生START和STOP条件,如果DW_apb_i2c 接收到读请求时,软件没有来得及把数据发送到 DW_apb_i2c 的TX_FIFO,则将SCL线保持为低电平,这会暂停I2C总线,直到读数据被提供给模块。

2.3.4 从机地址模式

DW_apb_i2c 支持 7bit 地址和10bit地址,见下图2-5 和图2-6。从机地址的介绍和使用请参考第一章。

对于第一个字节的专用地址和保留地址,DW_apb_i2c 也有介绍,与第一章 I2C介绍中内容保持一致。详细说明见下表2-1。DW_apb_i2c 并不限制使用这些保留地址,但是在使用这些预留地址时,可能会遇到与其他I2C组件不兼容的问题。

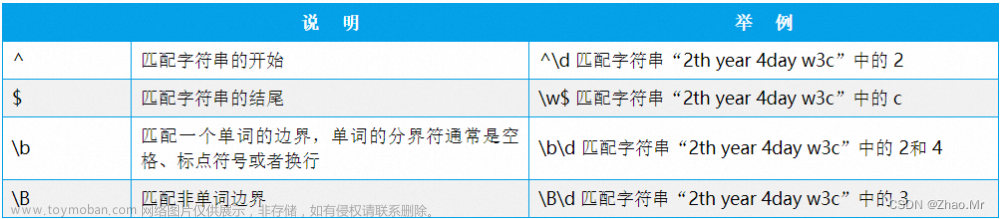

2.3.5 输入滤波功能

DW_apb_i2c 包含可编程输入滤波逻辑,可对输入信号(SCL和SDA)进行毛刺过滤。每个输入信号(SCL和SDA)都有一个单独的计数器,该滤波逻辑基于监视输入信号(SCL和SDA)的计数器,检查输入信号在内部采样之前是否在设定的ic_clk周期内(即滤波周期)保持稳定,如果保持稳定,即认为是稳定输入信号,此时内部信号会更新,计数器重置并停止工作,在检测到新的输入信号之前,计数器不会重新启动;如果无法保持稳定,在计数器达到其计数周期之前,输入信号再次改变,则认为输入信号是毛刺信号,当这种情况发生时,计数器被重置并停止,内部信号不会更新(即毛刺信号被滤掉),计数器重置并停止工作,在检测到新的输入信号之前,计数器不会重新启动。

滤波周期是软件可以编程的,DW_apb_i2c 设计了3个寄存器,分别对应在不同速率模式下实现滤波功能。

(1)Standard mode (0 to 100 Kb/s)、Fast mode (≤ 400 Kb/s) 、Fast mode plus (≤ 1000 Κb/s)

配置 IC_FS_SPKLEN 控制滤波周期,I2C协议规定,该模式下最大滤波时间为50ns;

(2)High-speed mode (≤ 3.4 Mb/s)

配置 IC_HS_SPKLEN 控制滤波周期,I2C协议规定,该模式下最大滤波时间为10ns;

(3)Ultra-Fast Speed Mode(≤ 5 Mb/s)

配置 IC_UFM_SPKLEN控制滤波周期,I2C协议规定,该模式下最大滤波时间为10ns;

上述*SPKLEN 寄存器能配置的最小值是1,当配置值小于1时,也是按照1写入。

如上图2-24所示,以ic_clk频率100MHz为例,则 ic_clk的周期是10ns。根据协议要求,当SCL 在 Standard mode 时,过滤毛刺的最大长度是50ns,则 IC_FS_SPKLEN 最大配置为5,即5个ic_clk的周期内的波动都会被当做毛刺过滤掉。由上图可知,SCL第1个上升沿过来时,内部计数器开始计数,当计数到3时,SCL就变成低电平,根据滤波规则,这段高电平输入就被认为是毛刺信号并被过滤掉,内部SCL保持不变,还是低电平,计数器重置并停止工作。接着SCL又变为高电平,计数器开始计数,当计数到5时,SCL还是高电平,根据滤波规则,这是一个稳定输入信号,内部SCL更新状态变为高电平,计数器重置并停止工作。

2.3.6 SCL速率配置

2.3.6.1 SCL 配置寄存器

DW_apb_i2c 作为Master时,在开始传输之前,要配置*SCL_LCNT和*SCL_HCNT寄存器,确保SCL速率符合实际需求。*SCL_LCNT和*SCL_HCNT寄存器仅用于作为Master模式时配置SCL时序,所以当DW_apb_i2c 仅作为Slave时,不需要配置*SCL_LCNT和*SCL_HCNT寄存器。*CNT 寄存器有如下8个,分别对应4种速率模式:

(1)Standard mode (0 to 100 Kb/s)

■ IC_SS_SCL_HCNT

■ IC_SS_SCL_LCNT

(2)Fast mode (≤ 400 Kb/s)

■ IC_FS_SCL_HCNT

■ IC_FS_SCL_LCNT

(3)Fast mode plus (≤ 1000 Κb/s)

■ IC_HS_SCL_HCNT

■ IC_HS_SCL_LCNT

(4)High-speed mode (≤ 3.4 Mb/s)

■ IC_UFM_SCL_HCNT

■ IC_UFM_SCL_LCNT

其中,HCNT 的配置值必须大于SPKLEN + 5,LCNT的配置值必须大于SPKLEN+7。

2.3.6.2 SCL 计算公式

DW_apb_i2c 作为Master时,产生的SCL信号的高电平时间和低电平时间,也受SCL线的上升时间和下降时间影响,如下图2-30所示。

SCL线的上升时间和下降时间因外部电路而异,比如:IO驱动的特性、上拉电阻的大小、SCL线上的总电容等。

在 DW_apb_i2c 的内部逻辑中,在产生SCL高电平时,由于计数器计数以及逻辑处理等原因,高电平长度是HCNT+SPKLEN+7;在产生SCL低电平时,由于计数器计数的原因,低电平长度是 LCNT+1。

(1)考虑外部电路的影响,结合上图2-30,计算HCNT和LCNT的公式如下:

SCL高电平时间=[(HCNT+ IC_*_SPKLEN +7)*ic_clk]+SCL_Fall_time

SCL低电平时间=[(LCNT+1)*ic_clk]-SCL_Fall_time+SCL_Rise_time

(2)不考虑外部电路的影响,结合上图2-30,计算HCNT和LCNT的公式如下:

SCL高电平时间=[(HCNT+ IC_*_SPKLEN+7)*ic_clk]

SCL低电平时间=[(LCNT+1)*ic_clk]

这里的 IC_*_SPKLEN 是上一节内容中提到的滤波时间。

2.3.6.3 SCL 实例计算

ic_clk频率以100MHz为例,当时钟频率确定后,不考虑外部电路的影响,假定I2C速率100Kbps,假设FS_ SPKLEN=5,计算出当前的HCNT和LCNT值:

- ic_clk周期为10ns

- SCL周期10000ns,占空比设定50%,高低电平各5000ns,则:

带入高电平公式有:(SS_SCL_HCNT+5+7)*10=5000,得到SS_SCL_HCNT=488;

带入低电平公式有:(SS_SCL_LCNT+1)*10=5000,得到SS_SCL_LCNT=499;

2.3.7 总线清除功能

DWC_apb_i2c支持总线清除功能。在时钟(SCL)或数据(SDA)线异常卡在低电平状态时,该功能将会尝试让数据(SDA)和时钟(SCL)线恢复正常,这是一种异常恢复机制,但是无法保证百分百让总线恢复正常。

2.3.7.1 SDA 恢复

在数据线(SDA)卡在低电平时,主机将发送最多9个时钟脉冲,尝试在这9个时钟内恢复总线,如果SDA线路在9个时钟脉冲内恢复,则主机发送STOP以释放总线;如果SDA线即使在第9个时钟脉冲之后也没有恢复,则只能使用硬件复位来复位总线。

2.3.7.2 SCL 恢复

在时钟线(SCL)卡在低电平时(例如由于电路的电气故障),没有有效方法克服这个问题的,只能使用硬件复位来复位总线。

2.3.8 DMA功能

DW_apb_i2c 支持DMA操作。关于DMA的操作,DW_apb_i2c 协议文档主要是介绍如何与 DW_ahb_dmac 配合使用(果然是一家人=_=)。关于DW_ahb_dmac 的使用,本文不做介绍,本文重点介绍如何使能DW_apb_i2c的DMA功能。

2.8.1 DMA 使能

要在DW_apb_i2c上启用DMA控制器,必须配置DMA控制寄存器:IC_DMA_CR,这样才能把握手信号发送到DW_ahb_dmac 。将1写入IC_DMA_CR 寄存器的 TDMAE 位字段可使能 DW_apb_i2c DMA发送数据;将1写入IC_DMA_CR寄存器的 RDMAE 位字段可使能 DW_apb_i2c DMA接收数据。

2.8.2 DMA水线设置

(1)发送数据水线设置

配置 IC_DMA_TDLR 寄存器,当 DW_apb_i2c TX_FIFO 中剩余的数据量达到或者低于这个水线的时候,就会发送 dma_tx_req 信号到 DW_ahb_dmac ,DW_ahb_dmac 就会搬运 brust_size 个数据到到 DW_apb_i2c 的TX_FIFO中,依次循环,直到搬运完设定的数据量。

(2)接收数据水线设置

配置 IC_DMA_RDLR 寄存器,当RX_FIFO中接收的数据量达到或者超过这个水线的时候,就会发送 dma_rx_req 信号到 DW_ahb_dmac ,DW_ahb_dmac 就会到 DW_apb_i2c 的RX_FIFO中搬走brust_size 个数据,依次循环,直到搬运完设定的数据量。

2.3.9 SDA 保持时间

I2C协议规范要求在 Standard mode 和 Fast mode下,SDA信号要保持300ns的时间;在Fast mode plus 和 High-speed mode 下,SDA要有足够长的保持时间覆盖SCL下降沿。

SCL和SDA信号在板级上有延迟,意味着该信号即使在I2C主机上满足保持时间要求,但在I2C从机处却不一定满足要求(反之亦然)。由于每个应用程序会遇到不同的板级延迟,DW_apb_i2c 包含一个软件可编程寄存器(IC_SDA_HOLD),用于动态调整SDA保持时间。

文章来源:https://www.toymoban.com/news/detail-741606.html

文章来源:https://www.toymoban.com/news/detail-741606.html

如上图 2-31所以,Bit[15:0]用于控制发送数据时SDA的保持时间。Bit[23:16]用于控制接收数据时SDA的保持时间。SDA_HOLD需要根据支持的速度模式进行配置,并且在 DW_apb_i2c 处于关闭时才可以配置。文章来源地址https://www.toymoban.com/news/detail-741606.html

到了这里,关于第二章 DW_apb_i2c 介绍的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!