专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

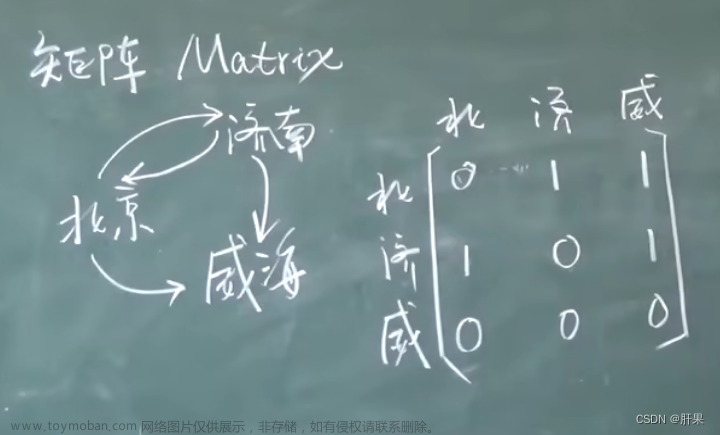

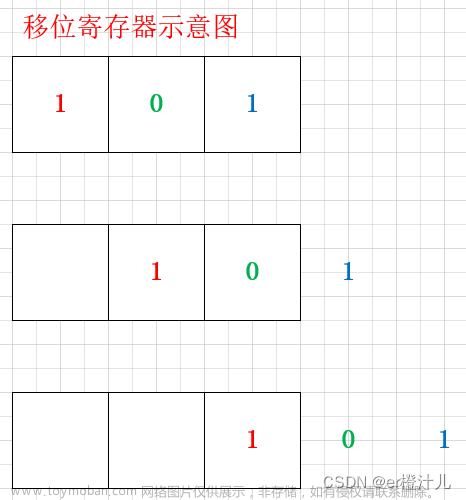

1、在硬件中进行乘除法运算是比较消耗资源的一种方法,想要在不影响延迟并尽量减少资源消耗,必须从硬件的特点上进行设计。根据寄存器的原理,由于是二进制,所以进位和退位为x2或者/2,同样除7可以使用进位3然后减去本身的做法,这样就将乘除法运算转化为位运算,这是一种比较简单的整数运算处理。

2、 需要给出一个计数器的状态机,注意d输入不是随时有效的,只有在cnt计数为0的那个时钟沿,d输入有效,因此需要设计一个寄存器din,在cnt为0时候锁存d的值

文章来源:https://www.toymoban.com/news/detail-745192.html

文章来源地址https://www.toymoban.com/news/detail-745192.html

`timescale 1ns/1ns

module multi_sel(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

//*************code***********//

reg [1:0] cnt ;

reg [7:0] din ;

always @ (posedge clk or negedge rst) begin

if (~rst) begin

cnt <= 0 ;

out <= 0 ;

input_grant <= 0 ;

din <= 0 ;

end

else begin

cnt <= (cnt + 1) % 4 ; // cnt <= cnt + 1 由于是2位的寄存器 溢出后自动清0 两种写法皆可

case (cnt)

0 : begin

din <= d ;

input_grant <= 1 ;

out <= d ;

end

1 : begin

input_grant <= 0 ;

out <= (din << 2) - din ;

end

2 : begin

input_grant <= 0 ;

out <= (din << 3) - din ;

end

3 : begin

input_grant <= 0 ;

out <= din << 3 ;

end

endcase

end

end

//*************code***********//

endmodule到了这里,关于「Verilog学习笔记」移位运算与乘法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!