#使用记录#

对于Quartus的安装步骤这里不再进行讲解,modelsim的安装步骤后续文章会进行讲解,这里也就不过多说明。言归正传,现在来开始我们的使用教程:

一、工程创建

1、首先点击打开Quartus软件,博主这里使用的是22版本的,其他版本的步骤也基本一样。

2、我们可以看到如下界面,点击新建工程

3、首先点击浏览,选择工程文件存放位置,然后修改工程名称,然后点击下方NEXT继续下一步

4、这不用管它直接默认选择空工程,然后点击NEXT

5、这里是添加文件,因为我们没有需要添加的,所以也不需要管,点击NEXT进入下一步就行

6、这里首先点击选择你需要的芯片的芯片包,然后再输入对应的芯片,最后在下面即可看到芯片,然后点击NEXT进入下一步

7、这里点击选择仿真方式以及编写程序使用的语言,选择完成点击NEXT进入下一步

8、点击Finish,工程创建就完成了

二、简单代码编写及下载

1、点击左上角File-->New新建,出现如下界面,选择你的文件类型,原理图输入就选择Block Diagram/Schematic File,我们这里使用代码输入,并且是Verilog HDL语言,所以选择Verilog HDL File然后点击OK。

2、再出现的界面输入代码,这里是一个测试代码,可以复制使用:

module example(

input clk,

input rst_n,

input data,

output pos_edge, //上升沿

output neg_edge, //下降沿

output data_edge, //数据边沿

output reg [1:0] D

);

//设置两个寄存器,实现前后电平状态的寄存

//相当于对dat_i 打两拍

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

D <= 2'b00;

end

else begin

D <= {D[0], data}; //D[1]表示前一状态,D[0]表示后一状态(新数据)

end

end

//组合逻辑进行边沿检测

assign pos_edge = ~D[1] & D[0];

assign neg_edge = D[1] & ~D[0];

assign data_edge = pos_edge | neg_edge;

endmodule

3、点击如下按钮编译程序

4、出现如下界面,点击Yes保存文件

5、这里保存的名字和前面的module名称一样,否则会报错

6、看到如下结果就是编译正常,没有问题

7、然后是绑定引脚,有两种方式可以点击上方Assignments再选择Pin Planner或者点击如图右边的按钮进行绑定,绑定结束再进行一次编译,没有出问题接下来就是下载程序到开发板

8、选择Tools下面的programmer,或者下图按钮

9、先点击下图1位置选择硬件连接,然后点击Auto Detect进行自动检测,做后点击Start等待上方Progress下载完成即可在开发板看到对应效果。

三、与Modelsim进行联合仿真

1、点击Processing-->Start-->Start test bench template writer,这时我们的文件夹之下已经有了一个example.vt文件

2、对刚才生成的文件进行修改(可以直接复制下面代码,注意名称),然后在编译一次

`timescale 1ns/1ns

module example_tb;

reg clk;

reg rst_n;

reg data;

wire pos_edge;

wire neg_edge;

wire data_edge;

wire [1:0] D;

example u1(

.clk(clk),

.rst_n(rst_n),

.data(data),

.pos_edge(pos_edge),

.neg_edge(neg_edge),

.data_edge(data_edge),

.D(D)

);

//产生时钟激励

initial clk = 1;

always #10 clk = ~clk;

//输入激励

initial begin

rst_n=0;

data=0;

#100;

rst_n = 1;

#50

data=1;

#201;

data=0;

#201;

data=1;

#101;

data=0;

#200;

$stop;

end

endmodule

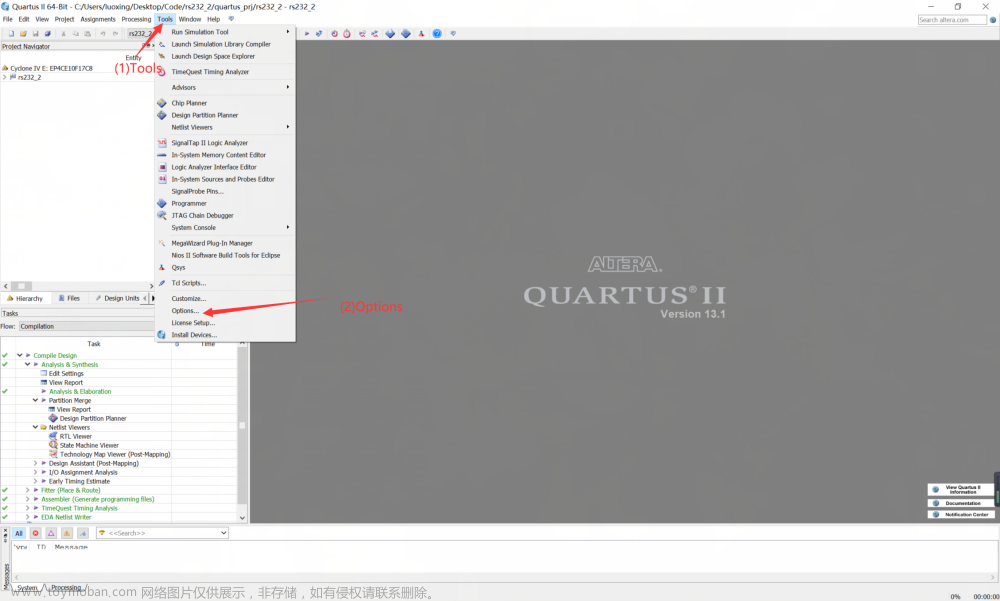

3、现在设置仿真,点击Tools-->Options-->EDA ToolsOptions选项,点击浏览Modelsim安装目录下的Win64或者Win32

4、然后对仿真文件设置点击Assignments-->Settings,再点击下面的Simulation按照如图设置

5、选择上面的Compile test bench点击后面Test Bench进入选择,点击New新建

6、按照顺序先编辑名字,然后浏览刚才的.vt文件,最后点击Add添加达到如下图效果,再点击OK,这里如果浏览的是.vo文件则后面仿真需要自己设置时间及电平,然后一直点击OK回到代码编辑界面

7、点击如下图按钮,然后点击仿真,会自动跳转Modelsim

8、选择下面的Wave即可看到波形,到这里就结束了

文章来源:https://www.toymoban.com/news/detail-751411.html

文章来源:https://www.toymoban.com/news/detail-751411.html

写在最后,希望文章可以帮到初学者,文章有不对的地方欢迎指出来一起学习,一起进步。文章来源地址https://www.toymoban.com/news/detail-751411.html

到了这里,关于Quartus使用步骤及联合Modelsim仿真教程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!