【Verilog HDL实践】8路彩灯控制程序

使用芯片:Altera Cyclone® IV EP4CE22F17C6N FPGA

开发工具:Quartus Ⅱ

开发项目:四、设计一个8路彩灯控制程序,要求彩灯重复显示以下6种演示花型,在演示过程中,只有当一种花型演示完毕才能转向其他演示花型。

(1)8路彩灯同时亮灭;

(2)从左至右逐个亮(每次只有1路亮);

(3)8路彩灯每次间隔1路灯亮,1路灯灭,且亮灭相间,交替亮灭。

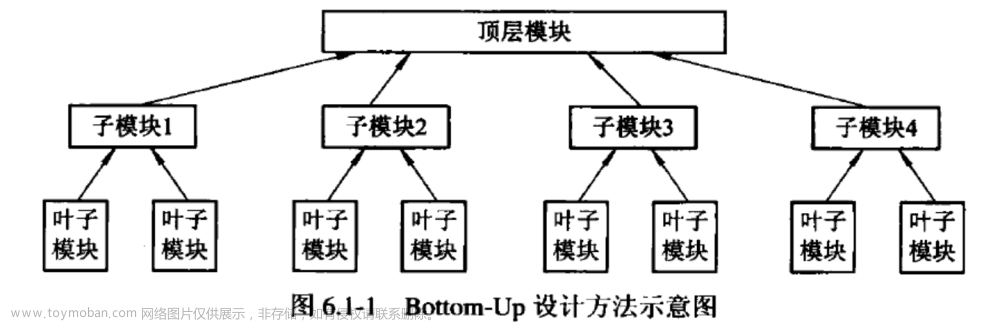

序列检测分析

使用状态机思想

共3种状态:

没有输入,当前状态演示完毕直接进入下一个状态即可。

代码展示

/*

模块功能:

四、设计一个8路彩灯控制程序,要求彩灯重复显示以下6种演示花型,在演示过程中,只有当一种花型演示完毕才能转向其他演示花型。

(1)8路彩灯同时亮灭;

(2)从左至右逐个亮(每次只有1路亮);

(3)8路彩灯每次间隔1路灯亮,1路灯灭,且亮灭相间,交替亮灭。

实现方法:

状态机:共3种状态,分别对应3种演示花型

以一定周期去切换状态。

考虑到第二种情况最少需要8个时钟周期,我们以8个时钟周期为一个大周期。

*/

module LED_control8(clk, areset, led);

input clk;

input areset;

output reg[7:0] led;

parameter[31:0] cycle = 32'd12500000;

reg[31:0] delay_counter;

reg delay_flag = 1'b0;

parameter style_one=2'b01, style_two=2'b10, style_three=2'b11;

parameter duration_style = 4'b1000; //每个演示样式耗费8个时间周期 0.8s

reg[3:0] duration_style_counter=4'b0000; //记录当前处于8周期中的哪个周期

reg[1:0] current_state=style_one, next_state=style_one;

reg[7:0] style_one_output=8'b0;

reg[7:0] style_two_output=8'b1;

reg[7:0] style_three_output=8'b01010101;

always@(posedge clk)begin

delay_counter <= delay_counter + 1'b1;

current_state <= next_state;

if(delay_counter >= cycle-1)begin

delay_flag <= ~delay_flag;

delay_counter <= 1'b0;

end

end

//各状态动作

always@(posedge delay_flag) begin

case(current_state)

style_one:begin

style_one_output<=~style_one_output;

led <= style_one_output;

duration_style_counter <= duration_style_counter + 1'b1;

if(duration_style_counter >= duration_style) begin

duration_style_counter <= 0;

next_state <= style_two;

end

end

style_two:begin

style_two_output<={style_two_output[6:0], style_two_output[7]};

led <= style_two_output;

duration_style_counter <= duration_style_counter+1'b1;

if(duration_style_counter >= duration_style) begin

duration_style_counter <= 0;

next_state <= style_three;

end

end

style_three:begin

style_three_output<=~style_three_output;

led <= style_three_output;

duration_style_counter <= duration_style_counter + 1'b1;

if(duration_style_counter >= duration_style) begin

duration_style_counter <= 0;

next_state <= style_one;

end

end

endcase

end

endmodule

代码流程比较简单,先引入一个500ms的定时器作为样式内的循环周期,如状态2需要从左至右逐个亮(共8路),故每次切换耗时500ms;同时规定一个样式最多消耗8个周期,即状态切换需要4秒。按顺序切换即可。文章来源:https://www.toymoban.com/news/detail-751812.html

时序测试

没做时序测试,烧入到开发板效果与预期一致。文章来源地址https://www.toymoban.com/news/detail-751812.html

到了这里,关于【Verilog HDL实践】状态机:8路彩灯控制程序的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!