在FPGA的设计中,往往要进行时序约束,时序约束的作用是告诉EDA软件,该设计要达到什么样的时序标准,在时序约束中,有着欠约束和过约束之分。

对于欠约束,就是约束的力度不够大,导致约束不足。

对于过约束,约束力度足够大,那么为什么也不行呢?假设FPGA中有三条线,这三条线要求都按照最大的频率去跑,到最后一个都跑不了(解释可能有问题,大概就是这个意思)

所以要合理的布局布线,不至于为了达到某一条路径的要求而牺牲掉其他路的资源。不能太高也不能太低

对于Quartus软件的操作:

假设我们的输入时钟频率为50MHZ

第一步:

运行程序,点击Time Quest Timing Analyzer选项,从里面的clock中,我们可以看出,系统默认的输入时钟频率为1000MHZ。从第二张图可以看出,整个系统可以正确传输数据的最大时钟频率应该是250.13MHZ,所以现在会报错(因为输入频率超出了最大频率).明明我们输入的频率是50MHZ,怎么变成了1000MHZ 了呢?

是因为你并没有告诉EDA软件,你是多大的时钟频率。所以在时序约束时,我们要告诉系统我们是多大的时钟频率。

文章来源地址https://www.toymoban.com/news/detail-751878.html

文章来源:https://www.toymoban.com/news/detail-751878.html

第二步:

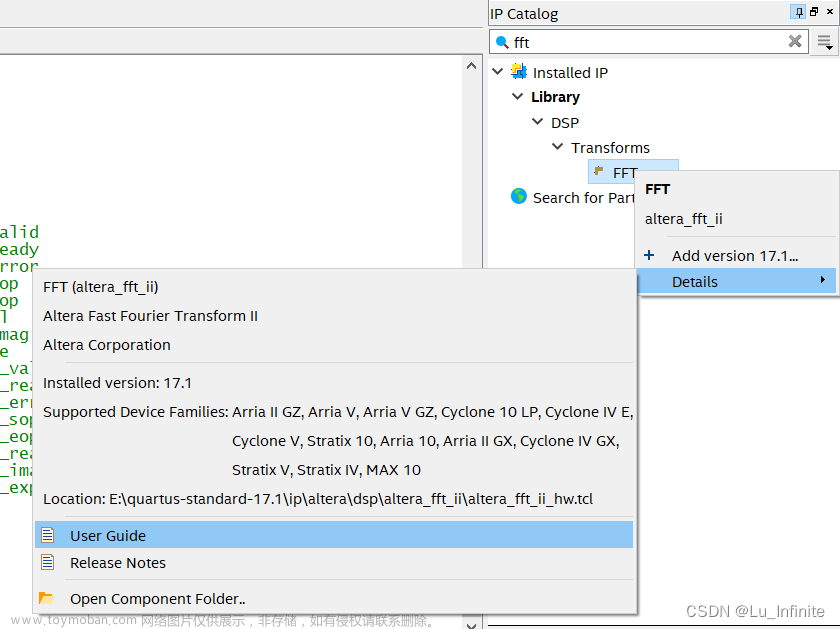

点击tools下的Time Quest Timing Analyzer,创建时序网表(create Timing Netlist)并且读取SDC文件(Read SDC File)

第三步:直接修改时钟

Task-----> Diagnostic下面的Report Clocks 双击

时钟的名字不用动,修改周期即可,同时Rising 和 Falling最好不填,因为这样可以自动匹配到合理的占空比

完成约束后,需要写SDC文件的操作,这个操作会生成包含所有约束的SDC文件,点击Write SDC File

重新运行代码,可以看到1000MHZ变成了50MHZ

到了这里,关于FPGA时序分析工具上手(一)(Quartus)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!