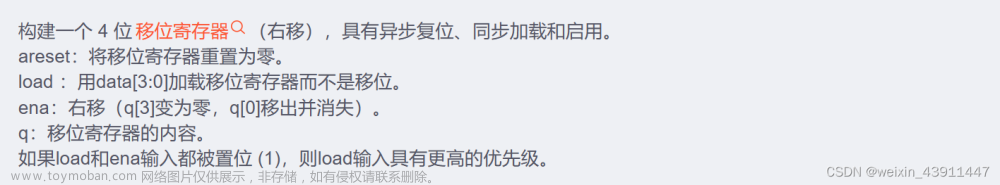

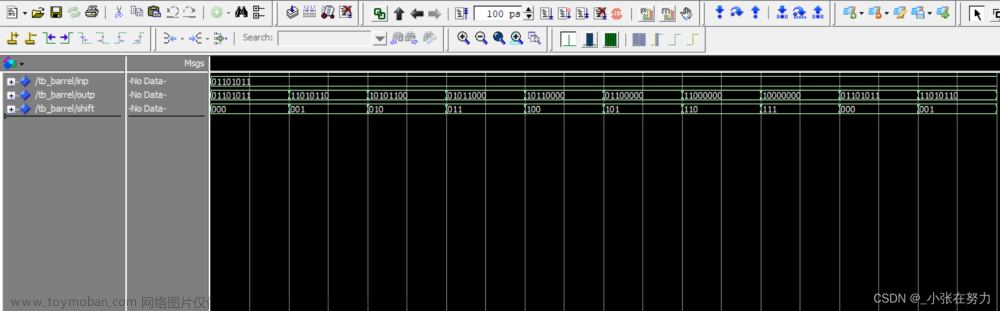

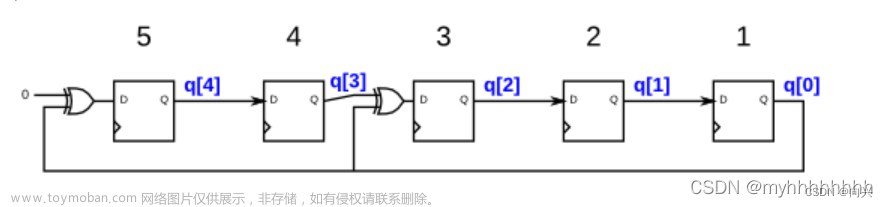

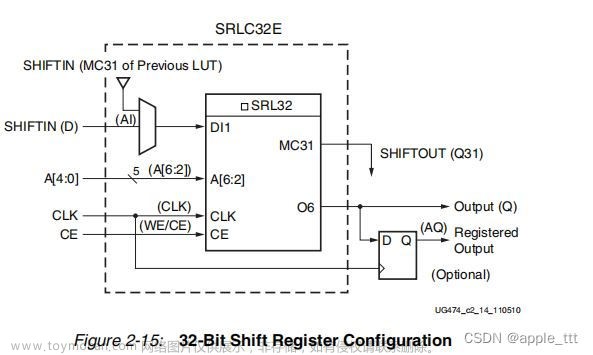

在Verilog中,你可以使用移位寄存器来实现数据的移位操作。移位寄存器是一种常用的数字电路,用于将数据向左或向右移动一个或多个位置。这在数字信号处理、通信系统和其他应用中非常有用。以下是一个使用Verilog实现的简单移位寄存器的示例:

module ShiftRegister (

input wire clk, // 时钟信号

input wire reset, // 复位信号

input wire shift_left, // 向左移位控制信号

input wire shift_right, // 向右移位控制信号

input wire data_in, // 输入数据

output wire data_out // 输出数据

);

reg [7:0] register; // 8位寄存器

always @(posedge clk or posedge reset) begin

if (reset) begin

// 复位时将寄存器清零

register <= 8'b0;

end else if (shift_left) begin

// 向左移位操作

register <= {register[6:0], data_in};

end else if (shift_right) begin

// 向右移位操作

register <= {data_in, register[7:1]};

end else begin

// 不进行移位,只存储输入数据

register <= data_in;

end

end

assign data_out = register; // 输出数据等于寄存器内容

endmodule

这个Verilog模块实现了一个8位移位寄存器。它接受时钟信号 clk,复位信号 reset,以及两个控制信号 shift_left 和 shift_right 以控制移位的方向。输入数据 data_in 被存储在寄存器中或者根据控制信号向左或向右移位。输出数据 data_out 是寄存器的当前内容。文章来源:https://www.toymoban.com/news/detail-752131.html

这个模块可以用于各种数字电路应用,包括数据的平行移位、数据的串行化和反串行化等。你可以根据具体需求修改位宽和控制信号来适应不同的应用场景。 Verilog的模块结构允许你方便地集成这个移位寄存器到更大的数字系统中。文章来源地址https://www.toymoban.com/news/detail-752131.html

到了这里,关于verilog——移位寄存器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!