目录

一.设计要求

二.模块总和

三.模块设计

1.顶层模块

2.分频模块

3.计数模块

4.倒计时模块

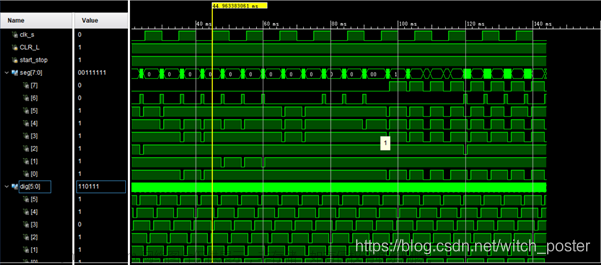

5.数码显示模块

6.管脚约束代码

四.引脚分配

五.演示视频

一、设计要求

①.用基于NEXY4 DDR开发板自带的时钟驱动电路,要求计时精确;

②.用开发板上的低 7 个开关(sw6-sw0),输入倒计时的初始秒数(最大 99);

③.用 2 个数码管以十进制显示当前的倒计时秒值;

④.用最高的开关(若开发板开关不够,可以用按键代替)实现 reset 功能;reset 后,能以 新的开关值进行倒计时。

⑤.当倒计时到 0 秒后,返回初始值继续倒计时。

二、模块总和

三、模块设计

1.顶层模块

module top(

input clk,

input rst_n,

input [6:0]sw,

output [7:0]sel,

output [7:0]seg

);

wire clk_1s;

wire [6:0]cnt;

wire [3:0]en1;

wire [3:0]en2;

div div(

.clk(clk),

.rst_n(rst_n),

.clk_1s(clk_1s)

);

count count(

.clk(clk_1s),

.rst_n(rst_n),

.sw(sw),

.cnt(cnt)

);

countdown countdown(

.clk(clk),

.rst_n(rst_n),

.cnt(cnt),

.en1(en1),

.en2(en2)

);

digital digital(

.clk(clk),

.rst_n(rst_n),

.en1(en1),

.en2(en2),

.seg(seg),

.sel(sel)

);

endmodule2.分频模块

module div(

input clk,

input rst_n,

output reg clk_1s

);

reg [29:0]counter1;//计数器技术满0.5ms需要30位宽的计数器

always @(posedge clk or negedge rst_n)

if(!rst_n)

counter1 <= 0;

else if(counter1 == 49999999)

counter1 <= 0;

else

counter1 <= counter1 + 1;

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1s <= 0;

else if(counter1 == 49999999)

clk_1s <= ~clk_1s;

else

clk_1s <= clk_1s;

endmodule3.计数模块

module count(

input clk,

input rst_n,

input [6:0]sw,

output reg [6:0]cnt //倒计时最大值99s

);

always @(negedge clk or negedge rst_n)

if(!rst_n)

begin

if(sw == 7'b000_0001)

cnt <= 7'd1;

else if(sw == 7'b000_0010)

cnt <= 7'd5;

else if(sw == 7'b000_0100)

cnt <= 7'd10;

else if(sw == 7'b000_1000)

cnt <= 7'd20;

else if(sw == 7'b001_0000)

cnt <= 7'd25;

else if(sw == 7'b010_0000)

cnt <= 7'd30;

else if(sw == 7'b100_0000)

cnt <= 7'd35;

else

cnt <= 0;

end

else if(cnt == 7'd99)

cnt <= 0;

else

cnt <= cnt + 1;

endmodule4.倒计时模块

module countdown(

input clk,

input rst_n,

input [6:0]cnt,

output reg [3:0]en1,//个位

output reg [3:0]en2//十位

);

always @(posedge clk or negedge rst_n)

if(!rst_n)

begin

en1 <= 0;

en2 <= 0;

end

else if(cnt <= 7'd99)

begin

en1 <= (99-cnt)%10;

en2 <= ((99-cnt)-en1)/10;

end

endmodule5.数码显示模块

module digital(

input clk,

input rst_n,

input [3:0]en1,

input [3:0]en2,

output reg [7:0]seg,

output reg [7:0]sel

);

//计数1ms

reg [16:0]counter2;//计数1ms 1000000/10= 100000

always @(posedge clk or negedge rst_n)

if(!rst_n)

counter2 <= 0;

else if(counter2 == 99999)

counter2 <= 0;

else

counter2 <= counter2 + 1;

//1ms时钟使能

reg clk_1ms_en;

always @(posedge clk or negedge rst_n)

if(!rst_n)

clk_1ms_en <= 0;

else if(counter2 == 99999)

clk_1ms_en <= 1;

else

clk_1ms_en <= 0;

//8位数码管计数器

reg [2:0]counter3;

always @(posedge clk or negedge rst_n)

if(!rst_n)

counter3 <= 0;

else if(clk_1ms_en)

counter3 <= counter3 + 1;

else

counter3 <= counter3;

//8位数码管选择

always @(posedge clk)

case(counter3)

0:sel <= 8'b1111_1110;

1:sel <= 8'b1111_1101;

2:sel <= 8'b1111_1111;

3:sel <= 8'b1111_1111;

4:sel <= 8'b1111_1111;

5:sel <= 8'b1111_1111;

6:sel <= 8'b1111_1111;

7:sel <= 8'b1111_1111;

endcase

wire[31:0]data;

assign data[3:0] = en1;

assign data[7:4] = en2;

reg [3:0]dsp_data;

always @(posedge clk)

case(counter3)

0:dsp_data <= data[3:0];

1:dsp_data <= data[7:4];

2:dsp_data <= data[11:8];

3:dsp_data <= data[15:12];

4:dsp_data <= data[19:16];

5:dsp_data <= data[23:20];

6:dsp_data <= data[27:24];

7:dsp_data <= data[31:28];

endcase

always @(posedge clk)

case(dsp_data)

4'd0:seg <= 8'b1100_0000;

4'd1:seg <= 8'b1111_1001;

4'd2:seg <= 8'b1010_0100;

4'd3:seg <= 8'b1011_0000;

4'd4:seg <= 8'b1001_1001;

4'd5:seg <= 8'b1001_0010;

4'd6:seg <= 8'b1000_0010;

4'd7:seg <= 8'b1111_1000;

4'd8:seg <= 8'b1000_0000;

4'd9:seg <= 8'b1001_0000;

endcase

endmodule

6.管脚约束代码

set_property IOSTANDARD LVCMOS33 [get_ports {seg[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sel[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

set_property PACKAGE_PIN C12 [get_ports rst_n]

set_property PACKAGE_PIN E3 [get_ports clk]

set_property PACKAGE_PIN J15 [get_ports {sw[0]}]

set_property PACKAGE_PIN L16 [get_ports {sw[1]}]

set_property PACKAGE_PIN M13 [get_ports {sw[2]}]

set_property PACKAGE_PIN R15 [get_ports {sw[3]}]

set_property PACKAGE_PIN R17 [get_ports {sw[4]}]

set_property PACKAGE_PIN T18 [get_ports {sw[5]}]

set_property PACKAGE_PIN U18 [get_ports {sw[6]}]

set_property PACKAGE_PIN U13 [get_ports {sel[7]}]

set_property PACKAGE_PIN K2 [get_ports {sel[6]}]

set_property PACKAGE_PIN T14 [get_ports {sel[5]}]

set_property PACKAGE_PIN P14 [get_ports {sel[4]}]

set_property PACKAGE_PIN J14 [get_ports {sel[3]}]

set_property PACKAGE_PIN T9 [get_ports {sel[2]}]

set_property PACKAGE_PIN J18 [get_ports {sel[1]}]

set_property PACKAGE_PIN J17 [get_ports {sel[0]}]

set_property PACKAGE_PIN H15 [get_ports {seg[7]}]

set_property PACKAGE_PIN L18 [get_ports {seg[6]}]

set_property PACKAGE_PIN T11 [get_ports {seg[5]}]

set_property PACKAGE_PIN P15 [get_ports {seg[4]}]

set_property PACKAGE_PIN K13 [get_ports {seg[3]}]

set_property PACKAGE_PIN K16 [get_ports {seg[2]}]

set_property PACKAGE_PIN R10 [get_ports {seg[1]}]

set_property PACKAGE_PIN T10 [get_ports {seg[0]}]四、引脚分配

文章来源:https://www.toymoban.com/news/detail-752133.html

文章来源:https://www.toymoban.com/news/detail-752133.html

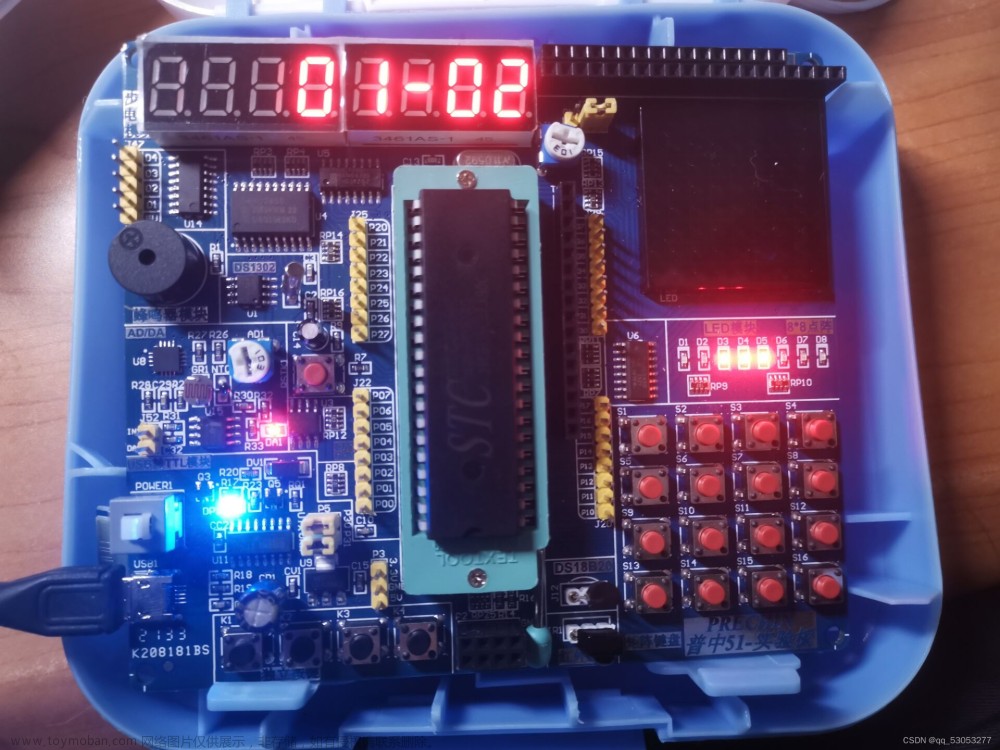

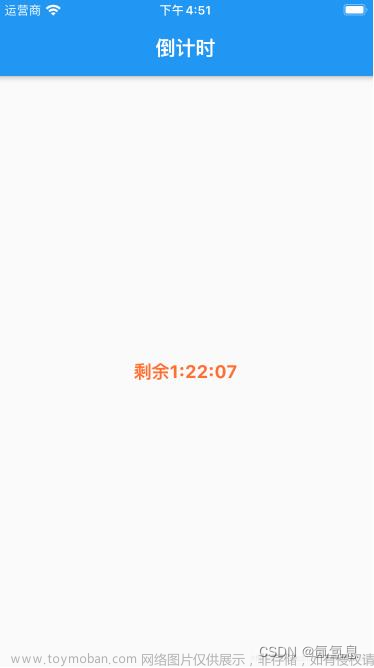

五、演示视频

IMG_2222文章来源地址https://www.toymoban.com/news/detail-752133.html

到了这里,关于Verilog设计倒计时秒表的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!