Ⅰ. 前置知识

0x00 并行加法器和减法器

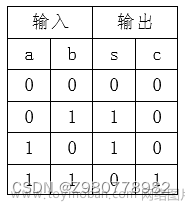

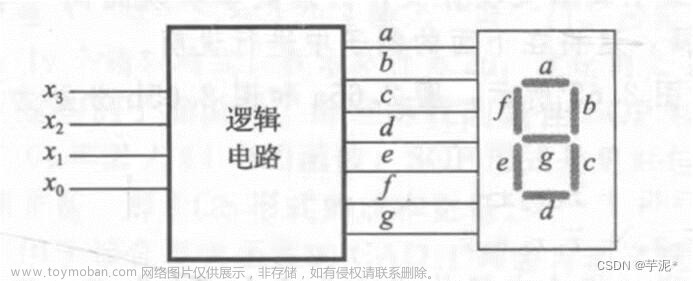

如果我们要对 4 位加法器和减法器进行关于二进制并行运算功能,可以通过将加法器和减法器以 N 个并行连接的方式,创建一个执行 N 位加法和减法运算的电路。

| 4 位二进制并行加法器 |

|

|

| 4 位二进制并行减法器文章来源地址https://www.toymoban.com/news/detail-752561.html |

到了这里,关于【FPGA】Verilog:二进制并行加法器 | 超前进位 | 实现 4 位二进制并行加法器和减法器 | MSI/LSI 运算电路的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

文章来源:https://www.toymoban.com/news/detail-752561.html

文章来源:https://www.toymoban.com/news/detail-752561.html