名称:VIVADO自动售票机售货机verilog代码ego1开发板验证

软件:VIVADO

语言:Verilog

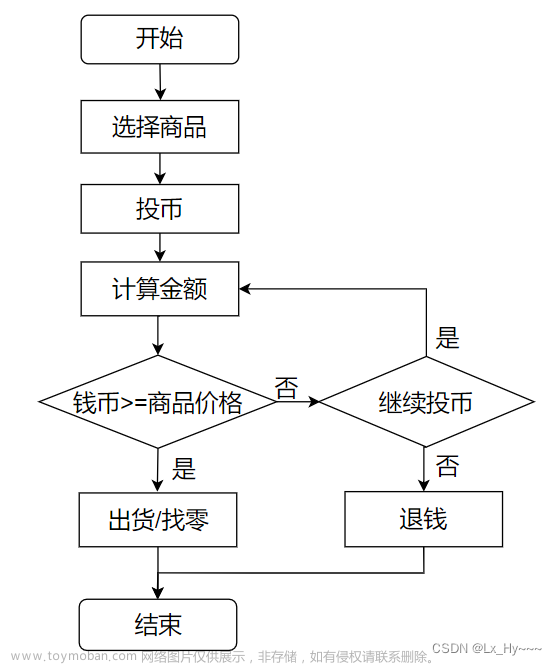

代码功能:

自动售票机

1、自动售票机只出售1角、2角、5角和1元4种车票

2、只接收1角、5角和1元硬币,每次只能出售1张车

3、自动售票机具有累加销售额的功能

实验要求

出售车票用SW0~3分别表示1角、2角、5角、1元4种 ;

投入硬币用S1、S2、S3分别表示1角5角和1元

投币后用开关SW7确认;若投入钱数不够,将硬币退出并报警,D9~D16闪烁,报警3秒

若投币足够,送出车票,用4个不同LED辅出D1、D2、D3、D4显示,若有余额自动找零

所有币额用两位BCD码显

按键和拔码开关需要做消抖处理。

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

代码下载:VIVADO自动售票机售货机verilog代码ego1开发板验证名称:VIVADO自动售票机售货机verilog代码ego1开发板验证 (代码在文末下载)软件:VIVADO语言:Verilog代码功能:自动售票机 1、自动售票机只出售1角、2角、5角和1元4种车票2、只接收1角、5角和1元硬币,每次只能出售1张车 3、自动售票机具有累加销售额的功能实验要求 出售车票用SW0~3分别表示1角、2角、5角、1元4种 ;投入硬币用S1、S2、S3分别表示1角5角和1http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=304

设计文档:

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 管脚分配

6. Testbench

7. 仿真图

整体仿真图

按键消抖模块仿真

售票机控制模块仿真

数码管显示模块仿真

文章来源:https://www.toymoban.com/news/detail-753490.html

文章来源:https://www.toymoban.com/news/detail-753490.html

部分代码展示:文章来源地址https://www.toymoban.com/news/detail-753490.html

//售货状态控制模块 module state_control( input clk_in, input rst,//高电平有效 //按键 高电平有效 input Selection_goods_01,//选商品1,商品分为0.1,0.2,0.5,1.0元 input Selection_goods_02,//选商品2,商品分为0.1,0.2,0.5,1.0元 input Selection_goods_05,//选商品5,商品分为0.1,0.2,0.5,1.0元 input Selection_goods_10,//选商品10,商品分为0.1,0.2,0.5,1.0元 input throw_into_10_down_out,//1.0元 input throw_into_05_down_out,//0.5元 input throw_into_01_down_out,//0.1元 input confirm_button_out,//确认 output [7:0] LED,//闪烁报警(D9~16) output reg outgo_done_01,//出货指示灯1 output reg outgo_done_02,//出货指示灯2 output reg outgo_done_05,//出货指示灯5 output reg outgo_done_10,//出货指示灯10 output [7:0] total_accumulated_money,//累计卖货额 output [7:0] total_throw_inmoney_out,//投入总钱币 output [7:0] total_need_money_out,//选中商品价钱 output [7:0] total_refund_money_out//找零金额 ); parameter state_0=4'd0;//选择商品 parameter state_1=4'd1;//投钱 parameter state_2=4'd2;//确认购买 parameter state_3=4'd3;//投入不足 parameter state_4=4'd4;//等待时间3秒 parameter state_5=4'd9;//结束 reg [3:0] state=4'd0; reg [7:0] total_throw_inmoney=8'd0;//投入总钱币 reg [7:0] total_need_money=8'd0;//选中商品价钱 reg [7:0] total_refund_money=8'd0;//找零金额 reg [7:0] accumulated_money=8'd0;//累计卖货额 assign total_throw_inmoney_out=total_throw_inmoney; assign total_need_money_out=total_need_money; assign total_refund_money_out=total_refund_money; assign total_accumulated_money=accumulated_money; ///控制模块:状态机,实现各个状态的转换// reg wait_second_time=1'd0; always@(posedge clk_in or posedge rst) if(rst) state<=state_0; else case(state) state_0://选择商品 begin if(confirm_button_out==1) begin state<=state_1; end else begin state<=state_0; end end state_1://投钱 begin if(confirm_button_out==1)//按确认键 state<=state_2;//找零 else state<=state_1;//继续投钱 end state_2://确认购买 begin if(total_throw_inmoney<total_need_money)//投入不足 state<=state_3;//蜂鸣器提示3秒 else begin //如果投入大于等于所需钱数 state <=state_4; end end state_3://投入不足,蜂鸣器提示 if(wait_second_time==1'd1) begin state<=state_0;//回到初始状态 end else begin state<=state_3; end state_4://等待时间3秒 if(wait_second_time==1'd1) //保持3s进入下一个状态 state<=state_5; else state<=state_4; state_5://结束 state<=state_0; default:state<=state_0; endcase

到了这里,关于VIVADO自动售票机售货机verilog代码ego1开发板验证的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!