序言

本文基于vivado的FPGA,对时序报红问题分析方法进行说明,并提供常见问题的解决办法。

时序报告

1.打开时序报告界面

(1)前提

先将工程进行综合和布局布线。

(2)方法1

IMPLEMENTION - Report Timing Summary

参数设置:

Maximum number of paths per clock or path group:每个时钟路径或者时钟组显示的最大路径数,想要查看的信号数越多,这个值就要设置更大,一般默认值10就可以了;

Maximum number of worst paths per endpoint:最坏路径数量,只用看最差路径的情况即可,保持默认值1即可。

设置好了值-点击OK

(3)方法2

在功能栏点击∑-在弹出的Project Summary界面的Timing框内-点击Implementation Timing Report

2.时序报告界面说明

(1)Timing界面

在弹出的Timing界面中,左侧是时序信息总览、时钟和时序路径分类,右侧是时序报告的详细信息,主要包含了三部分Setup、Hold以及Pulse Width,对应建立时间、保持时间和脉冲宽度三部分的时序违例说明:

具体参数:

WNS (Worst Negative Slack) :最差负时序裕量

TNS(Total Negative Slack) :总的负时序裕量 ,也就是负时序裕量路径之和

WHS (Worst Hold Slack) :最差保持时序裕量

THS (Total Hold Slack) :总的保持时序裕量,也就是负保持时序裕量路径之和

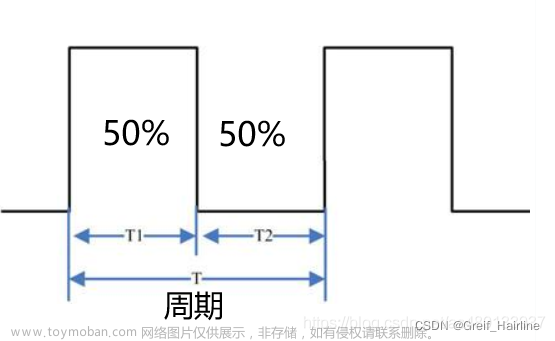

WPWS (Worst Pulse Width Slack) :最差脉冲宽度时序裕量

TPWS (Total Pulse Width Slack) :总的脉冲宽度时序裕量,也就是负脉冲宽度时序裕量路径之和

注意:显示为红色表示存在时序违例

(2)时序违例分析位置

点击WNS 、WHS或者WPWS就会弹出对应时序问题最严重的信号界面:

主要参数:

Name:路径名;

Slack:时间裕量;

Levels:组合逻辑级数,表示两个寄存器之间存在的组合逻辑层数

High Fanout:高扇出数,表示一个信号驱动的所有接收端的数量

From:路径起始位置,包含HDL代码中的起始寄存器

To:路径结束位置,包含HDL代码中的起始寄存器的下一级寄存器

Total Delay:整个路径的总体延时

Logic Delay:整个路径的逻辑延时

Source Clock:路径起始寄存器的时钟

Destination Clock:路径终点寄存器的时钟

Requirement:时钟周期,即路径延时最大值

3.常见的时序违例问题及解决办法

(1)建立时间问题

A)问题一:两个寄存器间组合逻辑级数层数过多

标志:2.(2)中Levels值过大,一般要求:逻辑级数≤时钟周期(ns)×2

解决办法:

方法1:

在Levels过大的位置,将组合逻辑使用寄存器进行打拍,即在两级寄存器中间位置插入一个寄存器;

方法2:

修改信号属性,使用Vivado 中提供的 retiming_forward 和 retiming_backward 属性来控制特定寄存器或路径上的最优化。使用这些属性会对一组特定路径(而不是顶层模块或子模块)应用重定时最优化,从而减少面积开销:

(*retiming_forward = 1 *) reg gt_reset;

(*retiming_backward = 1 *) reg gt_reset;

B)问题二:信号扇出数过高,即信号驱动的接收端数量过多

标志:2.(2)中High Fanout值过大

解决方法:

方法1:手动减少对应信号驱动接收端的数量;

方法2:设置信号属性,通过设置信号扇出数的上限,让综合器自动优化;(这种方法的基本原理同1是一样的,不同的是这种方法是vivado综合时自动实现的)

方法3:BUFG,一般用于时钟和复位信号的高扇出问题,但是BUFG资源有限,一般不用于解决普通信号的高扇出问题。

set_property CLOCK_BUFFER_TYPE BUFG [get_nets netName]

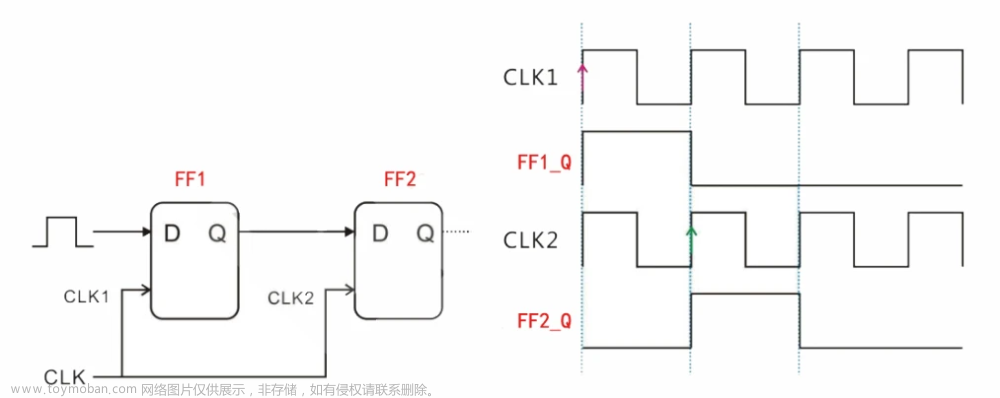

(2)保持时间问题

A)规范进行跨时钟域传输数据

后续会出跨时钟域数据传输的具体方法合集,这里不再赘述。

(3)通用方法

A)删除ILA(很重要)

ILA是最容易造成时序报红的原因之一,在代码完成后且不需要观测信号后,将所有ILA代码删除或者注释掉。

B)修改综合策略(这种方法一般不能完全解决问题)

操作:在任务栏点击∑-在Project Summary界面中的Synthesis框中点击Strategy后面的蓝色字体-在弹出的下示界面进行策略修改 文章来源:https://www.toymoban.com/news/detail-754283.html

文章来源:https://www.toymoban.com/news/detail-754283.html

策略选择(Options):

Strategy:包含多种综合策略,也可以自定义策略:

Flow_AreaOptimized_high:执行常规面积优化,包括强制执行三进制加法器,在比较器中使用新阈值以使用进位链以及实现面积优化的多路复用器;

Flow_AreaOptimized_medium:执行常规面积优化,包括更改控制集优化的阈值,强制执行三进制加法器,将推理的乘法器阈值降低到DSP模块,将移位寄存器移入BRAM,在比较器中使用较低阈值以使用进位链,以及进行区域优化的MUX操作;

Flow_AreaMultThresholdDSP:专用DSP块推断的下限阈值;

Flow_AlternateRoutability:使用算法提高布线能力,减少MUXF和CARRY的使用;

Flow_RuntimeOptimized:执行较少的时序优化,并消除一些RTL优化以减少综合运行时间。

下面的具体参数也可以调整,具体参数调整大家查一下资料,这里不再赘述:

C)修改IP核参数(针对IP核内部信号报红)

有的IP核需要选择资源最优还是速度最优时,选择速度最优(speed)。文章来源地址https://www.toymoban.com/news/detail-754283.html

到了这里,关于【FPGA】基于vivado FPGA设计过程中时序报红的分析及解决办法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!