1、打开软件,点击file->new project,新建工程

2、设置FPGA芯片的相关信息,需要与自己所使用的FPGA芯片信息保持一致(1~4),然后设置综合与仿真工具(即5和6,二者基本不变),随后就是自己所使用的硬件描述语言(7)。其中,步骤1到4参考下面第二张图

3、这里是之前编辑的汇总,直接finish就行

4、新建源文件

5、选择文件类型,填写文件名,然后一路next和finish下去

6、填写代码

7、开始编译,成功后可生成原理图

8、原理图生成完成,表示编译成功

9、开始功能仿真,此时需要新建一个仿真文件,后面同样一路next和finish

10、系统自动生成仿真文件内容,可以稍作修改,比如将所有情况枚举出来(下图中未作修改)

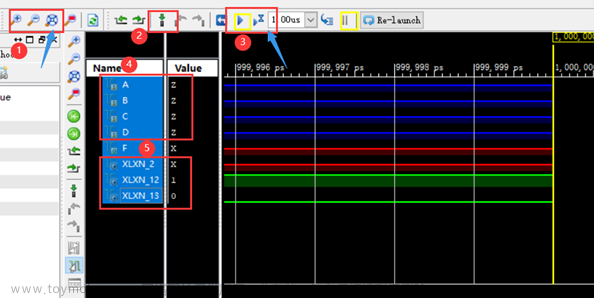

11、开始仿真,此处也可直接双击(后续所有节点操作都可),等待结果

12、观察弹出来的时序窗口,并且可以在下方控制台中输入代码,如run 1ms,直接回车。图中可以看出,abc均为低电平,因为0+0=0,所以仿真结果无误

13、仿真结束后,可以开始板级仿真,如下方式打开引脚约束(配置)截面,弹出来的小窗口全部点击yes和close

14、打开的窗口如下所示

15、设置对应的引脚与电平(此处随意设置),保存后关闭软件

16、此时可以看到,已经生成了对应的ucf文件,打开后如图所示

17、回到之前的界面,准备布局布线和生成FPGA可识别的bit文件,此处等待时间较长

18、完成后界面如图

19、开始准备配置设备的连接,如下点击,遇到小窗口,直接点击OK

20、出现的配置界面如下

21、双击Boundary Scan

22、在空白处右击,如下选择(此时需要先将FPGA与上位机连接好)

23、若是连接好,直接出现下面的结果,表示身份识别成功,4处直接点击yes

24、然后出现如下界面,直接找到自己之前生成的bit文件,点击open

25、然后出现这个界面,表示是否下载到flash中,若点击yes,意味着FPGA掉电后程序依旧存在,本人此处选择No

26、直接OK

27、右击,选择program,表示开始下载程序

28-1、出现如下情况,表示信号线路不一定完整,可以查看是否JTAG接错线,或者接触不良,或者参考以下链接:

https://electronics.stackexchange.com/questions/112415/the-idcode-read-from-the-device-does-not-match-the-idcode-in-the-bsdl-file

https://support.xilinx.com/s/article/13529?language=en_US#:~:text=If%20both%20Initialize%20Chain%20and%20Get%20Device%20IDCODE,opened%20or%20if%20the%20devices%20were%20added%20manually. 文章来源:https://www.toymoban.com/news/detail-754756.html

文章来源:https://www.toymoban.com/news/detail-754756.html

28-2、如下情况,表示下载成功

文章来源地址https://www.toymoban.com/news/detail-754756.html

文章来源地址https://www.toymoban.com/news/detail-754756.html

到了这里,关于ISE 14.7基础使用方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!