随着数字电子技术的不断发展,基于FPGA(现场可编程门阵列)的数字时钟设计方案逐渐成为了一种流行的选择。本篇博客将详细介绍如何利用FPGA实现一个简单的数字时钟,涉及到分频器、数码管驱动、时分秒计数、三八译码器和扫描数码管等模块。

1. 系统设计概述

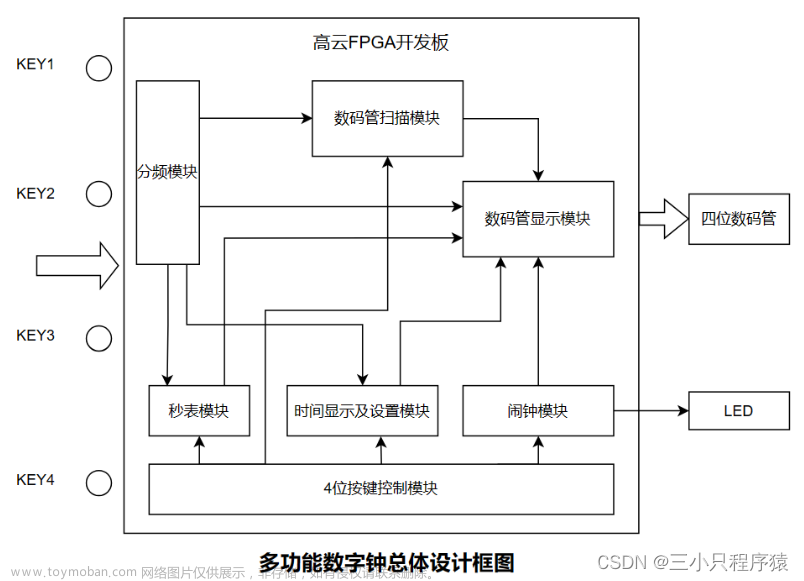

在本设计中,我们将使用FPGA来实现一个基本的数字时钟系统。该系统将包括一个时钟模块,用于产生时钟信号;计数器模块,用于计时;数码管显示模块,用于显示时、分、秒信息;以及控制逻辑模块,用于协调各个模块之间的工作。

2. 分频器设计

分频器是数字时钟系统中一个重要的模块,它用于将高频的时钟信号分频得到我们需要的低频时钟信号,例如1Hz的信号用于秒表计数。我们可以使用计数器对原始时钟信号进行计数,当计数到一定值时输出一个脉冲,从而实现分频。FPGA内部资源丰富,可以轻松实现各种分频比。

3. 数码管驱动设计

为了在数码管上显示时、分、秒信息,我们需要设计一个数码管驱动模块。这个模块可以将计时器模块输出的数字信息转换成数码管的段选信号和位选信号,并将其输出到数码管上。通过适当的时序控制,我们可以实现数码管上数字的刷新,实现动态显示。

4. 时分秒计数模块

时分秒计数模块负责对时间进行计数,并根据分频器模块提供的时钟信号进行更新。这个模块需要实现秒数的累加,分钟和小时的进位等逻辑。可以使用FPGA内部的计数器资源来实现这些功能,并利用逻辑电路来处理进位逻辑。

5. 三八译码器

为了将计数器模块输出的数字信号转换成数码管的段选信号,我们需要使用三八译码器。这个模块将会将4位的输入信号转换成7位的段选信号,用于驱动数码管的显示。可以使用FPGA内部的Look-up Table(LUT)来实现这个功能。

6. 扫描数码管

为了在多个数码管之间进行切换并依次显示时、分、秒信息,我们需要设计一个扫描数码管的模块。这个模块可以在不同的数码管之间进行快速切换,并配合数码管驱动模块实现连续的动态显示。可以使用FPGA内部的时序控制逻辑来实现数码管的扫描功能。

7. 控制逻辑设计

控制逻辑模块用于协调各个模块之间的工作。它可以接收来自分频器和计数器模块的信号,并根据需要控制数码管驱动模块和扫描数码管模块的工作。可以使用FPGA内部的状态机或者逻辑电路来实现这个模块。

8. 实现与验证

在完成所有模块的设计后,我们需要将这些模块进行集成,并利用FPGA开发工具进行编译、综合、布局和配置。完成后,我们可以通过观察数码管上的数字变化来验证时钟系统的正确性。

9. 总结

通过以上模块的设计与实现,我们可以在FPGA上构建一个简单的数字时钟系统。FPGA具有灵活性强、资源丰富的特点,非常适合于此类数字逻辑设计。同时,该设计还可以作为初学者学习数字逻辑和FPGA编程的一个很好的示例。

希望通过本篇博客的介绍,读者能够对基于FPGA的数字时钟设计有一个全面的了解,并能够进一步深入研究和实践。通过自己动手设计和实现一个数字时钟系统,可以加深对数字电子技术和FPGA编程的理解,同时也为日常生活中的实际应用打下基础。文章来源:https://www.toymoban.com/news/detail-754916.html

项目地址文章来源地址https://www.toymoban.com/news/detail-754916.html

到了这里,关于基于FPGA的数字时钟设计与实现(含源码)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!