在FPGA开发过程中,仿真是验证设计的重要环节。在Vivado设计套件中,我们可以使用仿真工具来验证设计的功能和性能。本文将介绍如何将Vivado仿真数据导出至.txt文件,以方便后续分析和处理。

步骤如下:

-

打开Vivado设计套件并创建一个新的工程。

-

在工程中添加设计文件和约束文件,完成设计的综合和实现。

-

在设计完成后,进入仿真阶段。选择仿真工具,例如XSIM。

-

在Vivado主界面的左下角选择"Open Elaborated Design",以打开设计的详细信息。

-

在仿真工具中,我们可以添加波形查看器来监视信号波形。选择"Add Wave"按钮,然后从设计中选择要监视的信号。

-

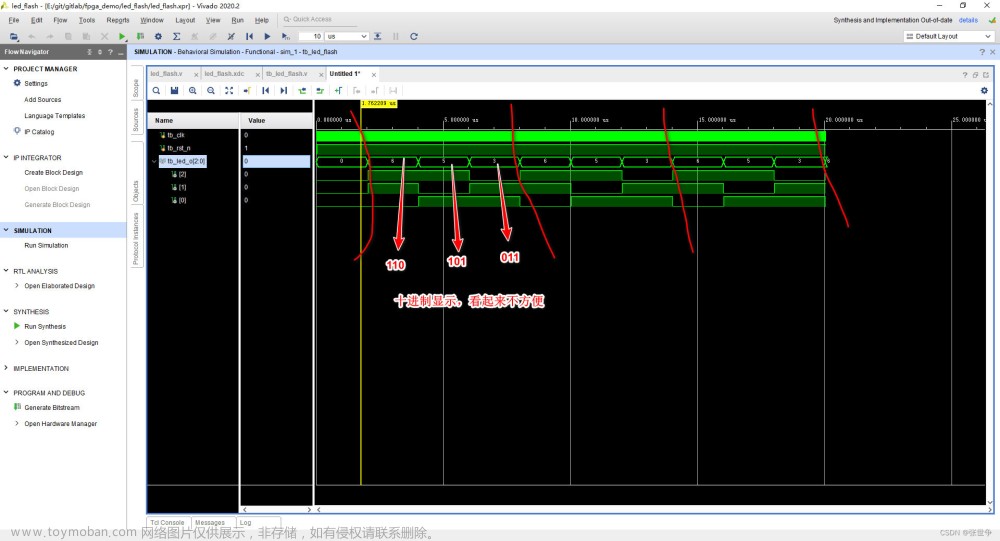

运行仿真以生成波形数据。在仿真工具的控制面板中,点击运行按钮开始仿真。仿真完成后,我们可以看到波形图中显示了各个信号的变化。

-

导出仿真数据。在仿真工具的控制面板中,选择"File" -> “Write VCD”,以将仿真数据导出为VCD文件。

-

打开终端或命令提示符窗口,并导航到Vivado项目的目录。文章来源:https://www.toymoban.com/news/detail-755143.html

-

在终端中运行以下命令,将VCD文件转换为txt文件:文章来源地址https://www.toymoban.com/news/detail-755143.html

xsim -gui <VCD文件名>.vcd write_wave -format txt <输出文件名>.txt exit ``` 这将使用XSIM命令行工具打开VCD文件,并将其转换为txt格式。请确保将"<VCD文件名>"替换为实际的VCD文件名,并将"<输出文件名>&

到了这里,关于Vivado仿真数据导出至.txt文件——FPGA开发的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!