实验四 QUARTUS开发环境实验

一、实验目的

1、通过实验,能熟悉QUARTUS开发环境,能够掌握QUARTUS的原理图输入法设计电路,掌握使用相关仿真工具进行功能和时序仿真的方法;

2、通过实验,加深对全加器电路的理解,并能使用QUARTUS的原理图输入法完成全加器的设计,并能在QUARTUS中完成相关的仿真验证;

二、实验原理

1、半加器、全加器的功能表见教材相关章节;

2、使用QUARTUS的原理图输入法完成半加器、全加器的设计,并能在QUARTUS中完成相关的仿真验证;

三、实验设备和器材

电脑、QUARTUS集成开发环境。

四、实验内容和步骤

4.1 半加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

1.写出1位半加器的功能表,设计出1位半加器的逻辑电路图(预习时自行完成);

2.在QUARTUS中使用原理图输入法,完成1位半加器电路的设计;

3. 在QUARTUS中完成对所设计1位半加器电路的功能仿真和时序仿真;

4.2 1位全加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

1.写出1位全加器的功能表,设计出1位全加器的逻辑电路图,要求使用4.1所设计的半加器实现(预习时自行完成);

2.在QUARTUS中使用原理图输入法,完成1位全加器电路的设计;

3. 在QUARTUS中完成对所设计1位全加器电路的功能仿真和时序仿真;

4.3 4位全加器

在QUARTUS器件库选择相关器件,完成下面实验内容;

1.写出4位全加器的功能表,设计出4位全加器的逻辑电路图,要求使用4.2所设计的半加器实现(预习时自行完成);

2.在QUARTUS中使用原理图输入法,完成4位全加器电路的设计;

3. 在QUARTUS中完成对所设计4位全加器电路的功能仿真和时序仿真;

五、实验记录和实验结果

5.1 半加器

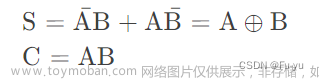

1.给出1位半加器的功能表,并给出设计出的1位半加器(请预习时完成)

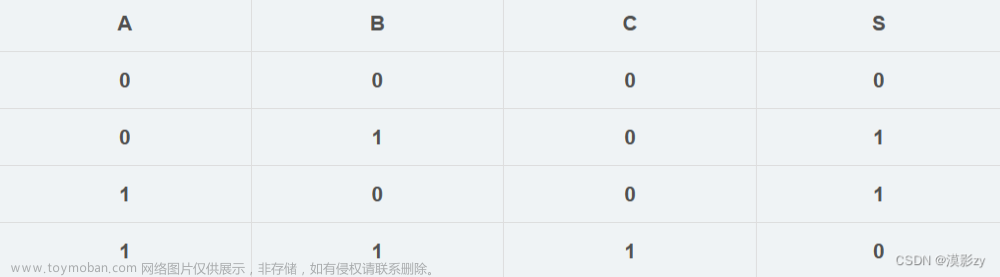

2.给出QUARTUS中使用原理图输入法实现1位半加器设计过程及电路

3.在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

功能仿真:

据图可知功能仿真符合半加器功能表

时序仿真:

据图可知时序仿真符合半加器功能表

所以半加器仿真成功

5.2 1位全加器

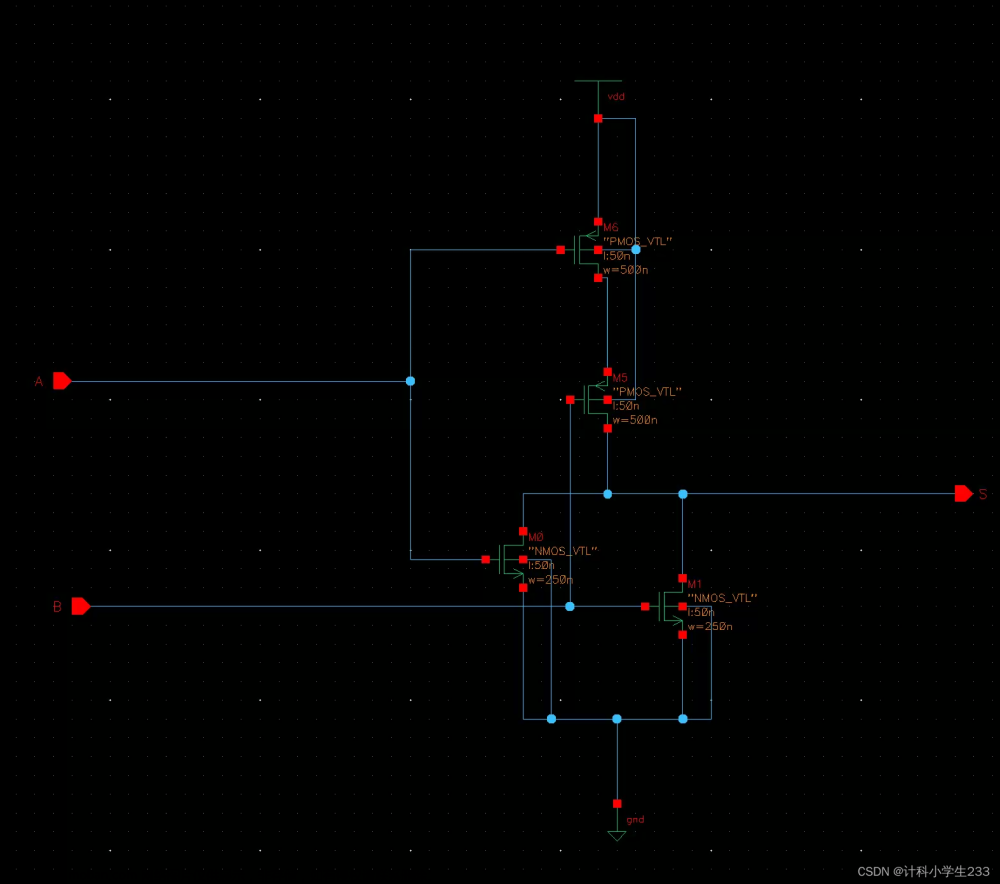

1.给出1位全加器的功能表,并给出设计出的1位全加器,要求使用前面设计的半加器(请预习时完成)

2.给出QUARTUS中使用原理图输入法实现1位全加器设计过程及电路

3.在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

功能仿真:

据图可知功能仿真符合全加器功能表

时序仿真:

据图可知时序仿真符合全加器功能表。

所以全加器仿真成功。

5.3 4位全加器

1.给出4位全加器的功能表,并给出设计出的4位全加器,要求使用前面设计的半加器(请预习时完成)

2.给出QUARTUS中使用原理图输入法实现4位全加器设计过程及电路

3.在所设计电路基础上,设计合理的输入信号,实现对所设计电路的功能仿真和时序仿真,要求简要说明仿真和验证思路,记录验证电路和输入信号,仿真结果及结论

功能仿真:

据图可知功能仿真符合四位全加器功能表。

时序仿真:

据图可知时序仿真符合四位全加器功能表。

所以四位全加器仿真成功。

六、实验预习要求

- 实验前认真阅读本实验指导;

- 熟悉quartus中相关操作及相关器件。

- 完成四和五中要求预习时完成的内容。

七、思考题。

在quartus完成对组合逻辑电路设计、功能仿真及验证的有哪些步骤?

1.根据任务的要求,列出真值表;

2.用卡诺图或代数化简法求出最简的逻辑表达式;

3.根据表达式,画出逻辑电路图,用标准器件构成电路;文章来源:https://www.toymoban.com/news/detail-755297.html

4.最后,用实验来验证设计的正确性。文章来源地址https://www.toymoban.com/news/detail-755297.html

到了这里,关于实验四 QUARTUS开发环境实验 设计半加器、全加器和四位全加器 blueee的学习笔记的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!