名称:数字式竞赛抢答器设计4路抢答器verilog

软件:Quartus

语言:Verilog

代码功能:

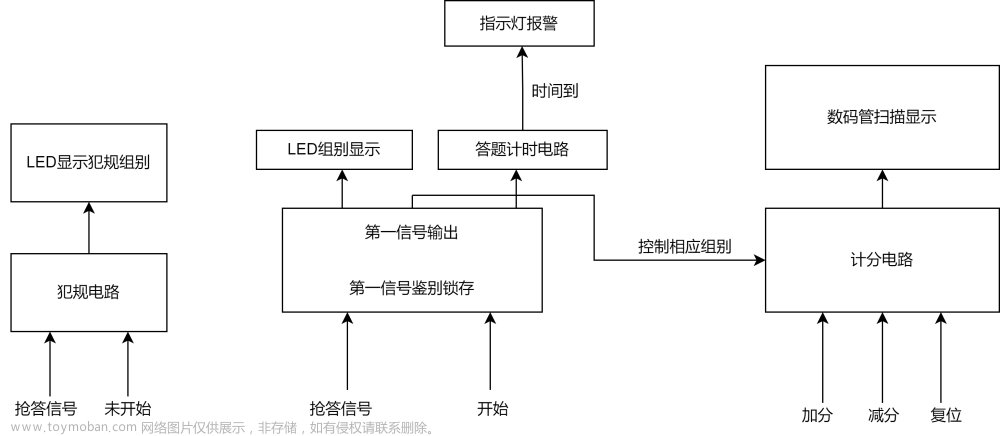

数字式竞赛抢答器设计

设计一个可容纳四组参赛者同时抢答的数字抢答器。

要求:

(1)能判断第一抢答者并报警指示抢答成功,其他组抢答均无效;

(2)设计倒计时时钟,若提前抢答则对相应的抢答组发出警报。

本代码已在AX301开发板验证,开发板资料:

AX301开发手册.pdf

FPGA代码资源下载网:hdlcode.com

代码下载:

数字式竞赛抢答器设计4路抢答器verilog_Verilog/VHDL资源下载名称:数字式竞赛抢答器设计4路抢答器verilog(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:数字式竞赛抢答器设计设计一个可容纳四组参赛者同时抢答的数字抢答器。要求:(1)能判断第一抢答者并报警指示抢答成功,其他组抢答均无效;(2)设计倒计时时钟,若提前抢答则对相应的抢答组发出警报本代码已在AX301开发板验证,开发板资料:AX301开发手册.pdf演示视频:部分代码展http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=190部分代码展示

//数字式竞赛抢答器设计 //设计一个可容纳四组参赛者同时抢答的数字抢答器。 //要求:(1)能判断第一抢答者并报警指示抢答成功,其他组抢答均无效; //(2)设计倒计时时钟,若提前抢答则对相应的抢答组发出警报 module qiangdaqi ( input clk,//50MHz input reset_n,//复位 input key_1,//抢答键 input key_2,//抢答键 input key_3,//抢答键 //input key_4,//抢答键 output alarm_LED,//高电平亮,提前抢答指示灯 output beep,//蜂鸣器,低电平响 output [5:0] bit_select,//数码管位选 output [7:0] seg_select//数码管段选 ); wire [3:0] number;//抢答编号 wire [3:0] time_downcnt;//倒计时 //控制模块 control i_control ( . clk(clk),//50MHz . reset_n(reset_n),//复位 . key_1(key_1),//抢答键 . key_2(key_2),//抢答键 . key_3(key_3),//抢答键 . key_4(1'b1),//抢答键 . alarm_LED(alarm_LED),//高电平亮,提前抢答指示灯 . beep(beep),//蜂鸣器,低电平响 . number(number),//抢答编号 . time_downcnt(time_downcnt)//倒计时 ); //数码管显示模块 display i_display( . clk(clk), . number(number),//抢答编号 . time_downcnt(time_downcnt),//倒计时 . bit_select(bit_select),//数码管位选 . seg_select(seg_select)//数码管段选 ); endmodule

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 管脚分配

6. Testbench

7. 仿真图

整体仿真

控制模块

显示模块

文章来源:https://www.toymoban.com/news/detail-755512.html

文章来源:https://www.toymoban.com/news/detail-755512.html

文章来源地址https://www.toymoban.com/news/detail-755512.html

文章来源地址https://www.toymoban.com/news/detail-755512.html

到了这里,关于竞赛抢答器4路抢答器verilog,仿真视频、代码、AX301开发板的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!