名称:任意进制计数器12进制计数数码管显示verilog代码

软件:VIVADO

语言:Verilog

代码功能:

设计一个12进制计数器,计数值00-11需要在数码管上显示,

时钟脉冲通过按键开关设计。

电路的输入信号en进行清零。

本代码可以修改为任意进制计数器,即修改计数控制模块的红框内代码,如下所示:

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在ego1开发板验证,开发板如下,其他开发板可以修改管脚适配:

代码下载:任意进制计数器12进制计数数码管显示verilog代码ego1开发板_Verilog/VHDL资源下载名称:任意进制计数器12进制计数数码管显示verilog代码(代码在文末下载)软件:VIVADO语言:Verilog代码功能:设计一个12进制计数器,计数值00-11需要在数码管上显示,时钟脉冲通过按键开关设计。电路的输入信号en进行清零。本代码可以修改为任意进制计数器,即修改计数控制模块的红框内代码,如下所示:FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com本代码http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=311

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

6. Testbench

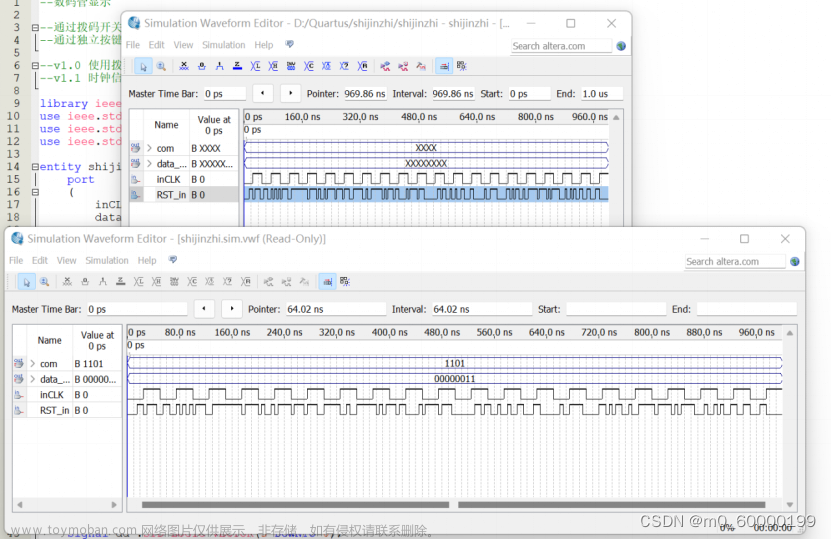

7. 仿真图

整体仿真图

按键模块

控制模块

显示模块

文章来源:https://www.toymoban.com/news/detail-756413.html

文章来源:https://www.toymoban.com/news/detail-756413.html

部分代码展示:文章来源地址https://www.toymoban.com/news/detail-756413.html

`timescale 1ns / 1ps //设计一个计数器 module shift_num( input clk_100M, input en_key,//清零 input shift_key,//手动按键 output [3:0] weixuan,//高选 output [7:0] duanxuan//高选 ); wire [7:0] num; wire shift_key_en; //按键消抖 key_jitter i_key_jitter( . clkin(clk_100M), . key_in(shift_key),//输入 . key_posedge(shift_key_en)//消抖后按键上升沿 ); //计数控制模块 shift_ctrl i_shift_ctrl( . clk(clk_100M), . en_key(en_key),//清零 . shift(shift_key_en),//手动按键 . num(num)//数 ); //数码管显示模块 display_drive i_display_drive( . clk(clk_100M), . num(num),//数 . weixuan(weixuan),//高选 . duanxuan(duanxuan)//高选 ); endmodule

到了这里,关于任意进制计数器12进制计数数码管显示verilog代码的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!