【FPGA显示驱动(Display)】- 使用Verilog实现8位数字显示器

FPGA是一种可编程的逻辑器件,它可以通过不同的配置来实现多种应用。在本文中,我们将探讨如何使用Verilog语言在FPGA上实现8位数字显示器。

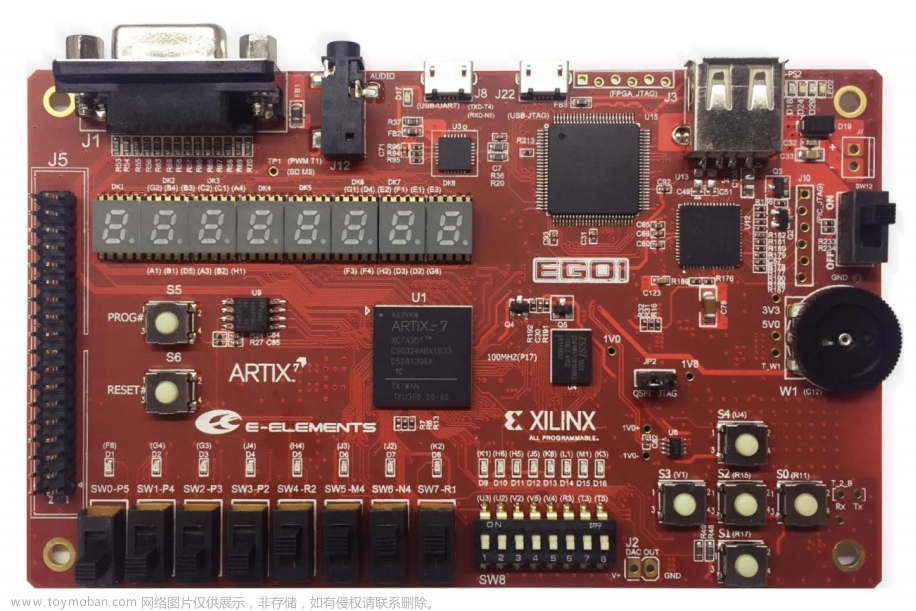

硬件环境

- Xilinx ISE Design Suite 14.7

- FPGA开发板

- 八段数码管

设计实现

在Verilog代码中,我们需要定义模块,并给出每个模块的输入输出端口,如下所示:

module display(

input [7:0] num, // 输入要显示的数字

output reg [7:0] seg, // 对应的8位七段数码管输出

output reg dp // 输出小数点(如果有的话)

);

然后,我们需要根据输入数字的不同,将其转换为对应的七段数码管输出。可以使用case语句或if-else语句来完成此操作。

我们可以使用以下真值表来指定每个数字所需的七段数码管输出:文章来源:https://www.toymoban.com/news/detail-759018.html

数字 | DP | A | B | C | D | E | F | G |

0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

2 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

3 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 |

4 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

5 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

6 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |文章来源地址https://www.toymoban.com/news/detail-759018.html

到了这里,关于【FPGA显示驱动(Display)】- 使用Verilog实现8位数字显示器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!