(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

前面讲解过一些时钟域的信号通过打拍的方式实现数据的同步,通过用地铁换乘的例子让大家理解了为什么信号的打拍可以实现不同时钟域信号的同步。

信号的打拍一般适用于单比特信号的跨时钟域处理,对于多比特的信号的跨时钟域处理一般不建议用打拍的方式。那多比特信号的跨时钟域处理一般用什么方式呢?这是面试常问的问题,笔者这儿可以告诉大家:常用的是异步缓存(fifo或者ram)同步,格雷码编码同步,还有就是今天笔者要讲的通过握手协议同步。

握手协议的跨时钟域处理就如快递员送快递一样,快递员把你的快递放入丰巢柜,然后短信通知你有快递;这时候快递处于未取件状态;当你扫描取件后,手机上会显示快递取件完成,同时也会通知快递员,丰巢柜又可以存放新的快递。

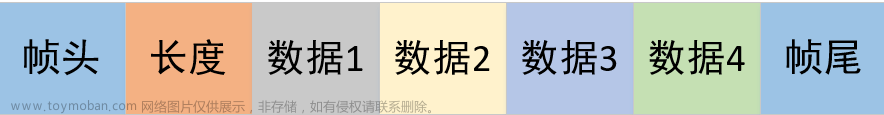

下面我们类比一下握手协议,当一个新的数据(快递)从时钟A端(快递员)往时钟B端(收货人)发送,数据先锁存起来(快递放入丰巢柜),时钟A端(快递员)发送req信号(取件码)通知时钟B端(收货人);时钟B端(收货人)收到req信号后,将锁存的数据取下来(从丰巢柜取快递),同时发送ack信号(快递已取件)给时钟A端(快递员),时钟A端(快递员)收到ack信号(快递已取件)后,就可以拉低req信号(取件码失效),准备发送新的数据。

上面的协议中是把多比特的数据锁存起来,通过单比特的req信号和单比特的ack信号控制数据的读写。其中req信号是从时钟域A到时钟域B,ack信号从时钟域B到时钟域A,用前面讲解的打拍同步即可。

来分析一下req信号拉高的条件,是时钟A端有新的数据要发送,将要发送的数据锁存,同时将req信号拉高;那req信号拉低的条件呢?是时钟A端收到了时钟B端发来的ack信号,就是时钟B端已经完成数据的接收。

再来看看ack信号拉高的条件,是时钟B端检测到req信号拉高,将时钟A端锁存的数据取出来,然后将ack拉高。那ack拉低的条件呢?是时钟B端检测到req信号拉低,即时钟B端知道时钟A端已经知道时钟B端完成数据的接收,有些绕口,这样解释一下:时钟B端完成数据接收是X,时钟A端知道X这个信息是Y,时钟B端知道Y这个信息是Z,那ack拉低的条件就是Z,也就是req拉低。

基于握手协议机制的跨时钟域同步实现简单,既适用于快时钟往慢时钟发送数据,也适用于慢时钟往快时钟发送数据。但是也有一个比较大的局限性,那就是发送的数据不能连续,也不能太快,必须在req拉低的时候才能开始一个新数据的发送。如果在req拉高的时候又来了新的数据,这个数据就会被丢掉。所以对于连续数据的跨时钟域同步一般是采用异步缓存的方式,异步缓存可以一次存储多个数据,也是通过req和ack完成同步,所以基于握手协议机制的跨时钟域同步是异步缓存跨时钟域同步的一个特例,就是每次发送的数据是一个!

原理介绍完,FPGA的实现就非常简单了,下面我们讲解一下。两个时钟域clk1和clk2,复位信号rst_n是低电平有效。din_en和din是clk1时钟域产生的数据相关的信号;dout_en和dout是clk2时钟域产生的数据相关的信号。gen_valid信号主要是用来指示新的数据可以发送了。

定义了所有需要的信号,要说明的一点是本时钟域的打拍一般用后缀dly,就是延时,比如din_en就是clk1时钟域的,也在clk1时钟域进行打拍;而不同时钟域的打拍一般用后缀sync,是同步,比如req_sync,req信号是clk1时钟域产生的,要到clk2时钟域内进行打拍。

din_en打拍主要是检测上升沿din_en_redge,一是用来锁存数据信号到din_latch,二是让req信号拉高。

req信号在din_en的上升沿拉高,在ack_redge的上升沿拉低,就是有新的数据拉高,对方完成这个数据的接收后拉低。ack信号是在clk2时钟域产生的,clk1时钟域要使用这个信号就要先同步到clk1的时钟域。

gen_valid就是用来指示新的数据可以发送了,req信号是clk1时钟域产生的,要在clk2时钟域内使用,那就要先同步到clk2时钟域。

ack信号在req信号的上升沿拉高,说明clk2时钟域已经收到clk1时钟域信息;在req信号的下降沿拉低,说明clk2时钟域已经收到clk1时钟域收到clk2时钟域完成数据接收的信息。同时产生clk2时钟域的数据相关信号dout_en和dout。

仿真的tb文件中,将clk1设置成50MHz,经clk2设置成100MHz,当然这个是可以任意设置的。新建了一个用来产生数据的task任务gen_data(),可以在gen_valid拉高的时候产生新的数据。

在run.do文件中加载了仿真的波形和仿真的时间,大家可以根据时间需求更改。

最后双击sim文件夹下的top_tb.bat文件即可以完成自动化的仿真。

截取了部分的仿真波形,输入信号和输出信号是一致的,功能正确。读者可以通过波形对功能进行更深刻的理解。

如果读者对设计或者仿真文件做了更改,只需要在命令行中输入do run.do即可重新仿真,不需要关闭软件重新双击top_tb.bat文件重新仿真。文章来源:https://www.toymoban.com/news/detail-759218.html

文章来源地址https://www.toymoban.com/news/detail-759218.html

文章来源地址https://www.toymoban.com/news/detail-759218.html

到了这里,关于孩子都能学会的FPGA:第十一课——基于握手机制的跨时钟域同步的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!