【Verilog HDL实践】汽车尾灯控制电路实现

使用芯片:Altera Cyclone® IV EP4CE22F17C6N FPGA

开发工具:Quartus Ⅱ

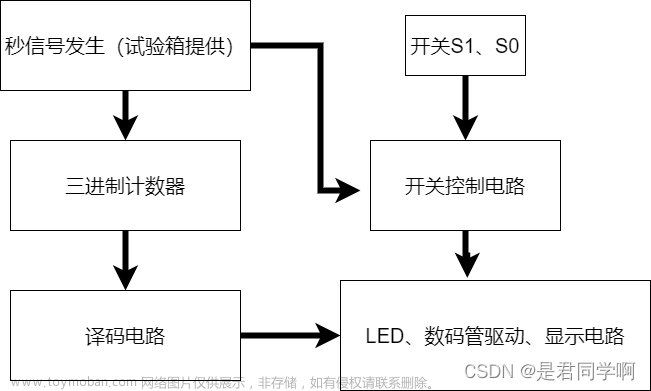

开发项目:设计一个汽车尾灯控制电路。已知汽车左右两侧各有3个尾灯,采用K0、K1进行状态控制,要求尾灯按如下规则亮灭。

(1)汽车沿直线行驶时,两侧的指示灯全灭; (KEY=2’b00)

(2)右转弯时,左侧的指示灯全灭,右侧的指示灯按000,100,010,001,000循环顺序点亮;(KEY=2’b01)

(3)左转弯时,右侧的指示灯全灭,左侧的指示灯按与右侧同样的循环顺序点亮;(KEY=2’b10)

(4)如果在直行时刹车,两侧的指示灯全亮;如果在转弯时刹车,转弯这一侧的指示灯按上述的循环顺序点亮,另一侧的指示灯全亮。(KEY=2’b11)

序列检测分析

使用状态机思想

共6种状态:

| 当前状态 | 当前输入 | 下一时刻输出 |

|---|---|---|

| 直行 | 00 | 直行 |

| 直行 | 10 | 左转 |

| 直行 | 01 | 右转 |

| 直行 | 11 | 直行时刹车 |

| 直行时刹车 | 00 | 直行 |

| 直行时刹车 | 10 | 左转 |

| 直行时刹车 | 01 | 右转 |

| 直行时刹车 | 11 | 保持 |

| 其他情况类似 |

代码展示

/*

模块功能:

设计一个汽车尾灯控制电路。已知汽车左右两侧各有3个尾灯,采用K0、K1进行状态控制,要求尾灯按如下规则亮灭。

(1)汽车沿直线行驶时,两侧的指示灯全灭; (KEY=2’b00)

(2)右转弯时,左侧的指示灯全灭,右侧的指示灯按000,100,010,001,000循环顺序点亮;(KEY=2’b01)

(3)左转弯时,右侧的指示灯全灭,左侧的指示灯按与右侧同样的循环顺序点亮;(KEY=2’b10)

(4)如果在直行时刹车,两侧的指示灯全亮;如果在转弯时刹车,转弯这一侧的指示灯按上述的循环顺序点亮,另一侧的指示灯全亮。(KEY=2’b11)

实现方法:

状态机:共六种状态:直行、左转、右转、直行刹车、左转刹车、右转刹车

以一定周期去检测按键情况,实现状态切换

*/

module Transport_led(clk, k0, k1, led);

input clk, k0, k1;

output reg[7:0] led;

parameter state_s=3'b000, state_l=3'b001, state_r=3'b010, state_ss=3'b011, state_ls=3'b100, state_rs=3'b101;//状态定义

parameter[31:0] duration = 32'd12500000; //timer:500ms

reg[2:0] current_state = state_s, next_state = state_s;

reg[31:0] counter = 32'b0;

reg delay_flag = 1'b0;

reg delay_flag2 = 1'b0;

reg[2:0] left_cycle = 3'b001;

reg[2:0] right_cycle = 3'b100;

//状态切换

always@(posedge clk) begin

current_state <= next_state;

counter <= counter + 1'b1;

if(counter >= duration-1) begin

counter <= 0;

delay_flag <= ~delay_flag;

delay_flag2 <= ~delay_flag2;

end

end

//下个状态变换

always@(posedge delay_flag) begin

case(current_state)

state_s: begin

if(~(k0|k1))

next_state <= state_ss;

else if(~k0)

next_state <= state_l;

else if(~k1)

next_state <= state_r;

end

state_l: begin

case({k1,k0})

2'b00: next_state <= state_ls;

2'b01: next_state <= state_r;

2'b10: next_state <= state_l;

2'b11: next_state <= state_s;

endcase

/*if(~(k0|k1))

next_state <= state_ls;

else if(~k1)

next_state <= state_r;

else if(k1&k0)

next_state <= state_s;

else

next_state <= state_l;*/

end

state_r: begin

case({k1,k0})

2'b00: next_state <= state_rs;

2'b01: next_state <= state_r;

2'b10: next_state <= state_l;

2'b11: next_state <= state_s;

endcase

/*if(~(k0|k1))

next_state <= state_rs;

else if(~k0)

next_state <= state_l;

else if(k1&k0)

next_state <= state_s;

else

next_state <= state_r;*/

end

state_ss: begin

if(k1&k0)

next_state <= state_s;

else if((k0==0) & (k1==0))

next_state <= state_ss;

else if(~k1)

next_state <= state_r;

else if(~k0)

next_state <= state_l;

end

state_ls: begin

if(k1&k0)

next_state <= state_s;

else if(~(k0|k1))

next_state <= state_ls;

else if(~k1)

next_state <= state_r;

else if(~k0)

next_state <= state_l;

end

state_rs: begin

if(k1&k0)

next_state <= state_s;

else if(~(k0|k1))

next_state <= state_rs;

else if(~k1)

next_state <= state_r;

else if(~k0)

next_state <= state_l;

end

endcase

end

always@(posedge delay_flag2) begin

case(current_state)

state_s: begin

led <= 8'b0;

end

state_l: begin

led <= {left_cycle, 5'b0};

left_cycle <= {left_cycle[1:0], left_cycle[2]};

end

state_r: begin

led <= {5'b0, right_cycle};

right_cycle <= {right_cycle[0], right_cycle[2:1]};

end

state_ss: begin

led <= 8'b11100111;

end

state_ls: begin

led <= {left_cycle, 5'b00111};

left_cycle <= {left_cycle[1:0], left_cycle[2]};

end

state_rs: begin

led <= {5'b11100, right_cycle};

right_cycle <= {right_cycle[0], right_cycle[2:1]};

end

endcase

end

endmodule

代码中引入一个500ms的定时器去定时检测按键k0、k1的电平状态,加以当前状态去判断下一时刻状态。文章来源:https://www.toymoban.com/news/detail-760436.html

时序测试

无论是时序测试还是烧入到开发板测试,结果都与预期情况一致。文章来源地址https://www.toymoban.com/news/detail-760436.html

到了这里,关于【Verilog HDL实践】汽车尾灯控制电路实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[蔡觉平老师主讲] Verilog HDL数字集成电路设计原理与应用](https://imgs.yssmx.com/Uploads/2024/04/848792-1.png)