Vivado硬件调试

ILA (Integrated Logic Analyzer)

集成逻辑分析仪:监控逻辑内部信号和端口信号。

一、例化ILA添加调试信号

-

添加IP核

-

根据要观测信号的属性设置探针属性

-

创建完成

-

例化模板

-

例化;

-

综合实现,生成bit流;

-

下载bit文件至开发板;

-

设置触发条件

-

抓取结果

抓取信号窗口的个数

等待抓取

抓取状态:

-

调试完后,删除例化的调试模块和IP核,重新生成bit文件。

二、综合后在网表里添加调试信号:

-

打开综合设计文件,调整窗口为Debug模式;

-

在”Nets“中选择要调试的信号,右键选择”Mark Debug“;

-

一些信号可能会被EDA优化,无法显示完整的数据位宽,此时需要在代码中修改,并重新综合。示例如下:

// 添加debug属性,此时EDA不会对该信号进行优化 (* mark_debug = "true" *)reg [24:0] counter; -

单击”Set Up Debug“

// xdc文件中多出来的完整代码: set_property MARK_DEBUG true [get_nets {Led_OBUF[0]}] set_property MARK_DEBUG true [get_nets {Led_OBUF[1]}] set_property MARK_DEBUG true [get_nets {Led_OBUF[2]}] set_property MARK_DEBUG true [get_nets {Led_OBUF[3]}] set_property MARK_DEBUG true [get_nets Rst_n_IBUF] create_debug_core u_ila_0 ila set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0] set_property ALL_PROBE_SAME_MU_CNT 1 [get_debug_cores u_ila_0] set_property C_ADV_TRIGGER false [get_debug_cores u_ila_0] set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila_0] set_property C_EN_STRG_QUAL false [get_debug_cores u_ila_0] set_property C_INPUT_PIPE_STAGES 0 [get_debug_cores u_ila_0] set_property C_TRIGIN_EN false [get_debug_cores u_ila_0] set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0] set_property port_width 1 [get_debug_ports u_ila_0/clk] connect_debug_port u_ila_0/clk [get_nets [list Clk_IBUF_BUFG]] set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe0] set_property port_width 4 [get_debug_ports u_ila_0/probe0] connect_debug_port u_ila_0/probe0 [get_nets [list {Led_OBUF[0]} {Led_OBUF[1]} {Led_OBUF[2]} {Led_OBUF[3]}]] create_debug_port u_ila_0 probe set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe1] set_property port_width 25 [get_debug_ports u_ila_0/probe1] connect_debug_port u_ila_0/probe1 [get_nets [list {counter[0]} {counter[1]} {counter[2]} {counter[3]} {counter[4]} {counter[5]} {counter[6]} {counter[7]} {counter[8]} {counter[9]} {counter[10]} {counter[11]} {counter[12]} {counter[13]} {counter[14]} {counter[15]} {counter[16]} {counter[17]} {counter[18]} {counter[19]} {counter[20]} {counter[21]} {counter[22]} {counter[23]} {counter[24]}]] create_debug_port u_ila_0 probe set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe2] set_property port_width 1 [get_debug_ports u_ila_0/probe2] connect_debug_port u_ila_0/probe2 [get_nets [list Rst_n_IBUF]] set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub] set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub] set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub] connect_debug_port dbg_hub/clk [get_nets Clk_IBUF_BUFG]可以直接在xdc文件中添加所要调试的信号探针。

-

“Open Hardware Manager”,连接开发板并下载程序;

-

调试完毕删除 xdc 文件中多余的代码和 3 中添加的代码,重新生成bit流;

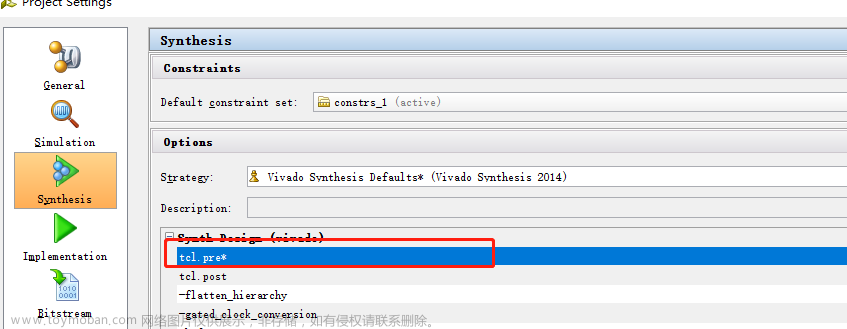

下载bit文件时,清除Debug文件的路径(图示);

VIO (Virtual Input/Output)

虚拟IO:实时监控和驱动逻辑内部信号和端口信号。文章来源:https://www.toymoban.com/news/detail-761090.html

VIO的使用参考Blog:VIVADO关于VIO IP核(Virtual Input/Output)的使用文章来源地址https://www.toymoban.com/news/detail-761090.html

到了这里,关于Vivado硬件调试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!