一、介绍

加法器和减法器是数字电路中的基本组件,它们可以对二进制数进行算术运算。加法器可以将两个或多个二进制数相加,得到一个和和一个进位。减法器可以将两个二进制数相减,得到一个差和一个借位。加法器和减法器可以用来实现更高级的运算,例如乘法、除法、移位等。

本报告的目的是使用Verilog语言编写一个位加法器(bit_add)和一个位减法器(bit_sub),并将它们组合成一个三位加法器(bit3_add)和一个三位减法器(bit3_sub)。本报告将介绍这些模块的设计和实现,以及它们的原理和功能。本报告还将分析这些模块的输入和输出,以及它们的优缺点。

二、设计和实现

1.位加法器(bit_add)

位加法器的原理是利用异或运算和与非运算来实现加法逻辑。异或运算可以判断两个输入是否相同,如果相同则输出0,如果不同则输出1。与非运算可以判断两个输入是否都为1,如果都为1则输出0,如果有一个为0则输出1。

位加法器的功能如下表所示:

位加法器(bit_add)是一个可以对两个一位二进制数和一个进位输入进行加法运算的模块,它有五个端口,分别是operand1、operand2、cin、result和cout。operand1和operand2是加数,cin是进位输入,result是当前位输出,cout是进位输出。

位加法器的代码如下:

module bit_add(operand1,operand2,cin,result,cout);

input operand1; // 加数1

input operand2; // 加数2

input cin; // 进位输入

output result; // 当前位输出

output cout; // 进位

wire c[3:0]; // 接线

// 当前位为三个输入的异或,三个输入为1的个数为奇数时,当前位为1

xor x1(c[0],operand1,operand2),

x2(result,c[0],cin);

// 进位信号为 与非(与非(输入1,输入2),与非(异或(输入1,输入2),进位))

nand na1(c[1],cin,c[0]),

na2(c[2],operand1,operand2),

na3(cout,c[1],c[2]);

endmodule

RTL分析图如下:

2.位减法器(bit_sub)

位减法器的原理是利用异或运算和与非运算来实现减法逻辑。异或运算可以判断两个输入是否相同,如果相同则输出0,如果不同则输出1。与非运算可以判断两个输入是否都为1,如果都为1则输出0,如果有一个为0则输出1。

位减法器的功能如下表所示:

位减法器(bit_sub)是一个可以对两个一位二进制数和一个借位输入进行减法运算的模块,它有五个端口,分别是operand1、operand2、cin、result和cout。operand1是被减数,operand2是减数,cin是借位输入,result是当前位输出,cout是借位输出。

位减法器的代码如下:

module bit_sub(operand1,operand2,cin,result,cout);

input operand1; // 被减数

input operand2; // 减数

input cin; // 借位输入

output result; // 当前位输出

output cout; // 借位

wire c[3:0]; // 接线

// 当前位为三个输入的异或,三个输入为1的个数为奇数时,当前位为1

xor x1(c[0],operand1,operand2),

x2(result,c[0],cin);

// 借位信号为 与非(与非(输入1,非输入2),与非(异或(输入1,非输入2),借位))

not n1(c[1],operand2);

nand na1(c[2],cin,c[0]),

na2(c[3],operand1,c[1]),

na3(cout,c[2],c[3]);

endmodule

RTL分析图如下:

3.三位加法器(bit3_add)

三位加法器的原理是利用位加法器(bit_add)来实现三位加法逻辑。三位加法器将两个三位二进制数的每一位和对应的进位输入分别送入位加法器,得到每一位的和和进位输出。三位加法器的最高位的进位输出就是整个三位加法器的进位输出。

串行进位加法器示意图如图:

三位加法器(bit3_add)是一个可以对两个三位二进制数和一个进位输入进行加法运算的模块, 它有九个端口,分别是operand1、operand2、cin、result和cout。operand1和operand2是加数,cin是进位输入,result是三位和,cout是进位输出。

三位加法器的代码如下:

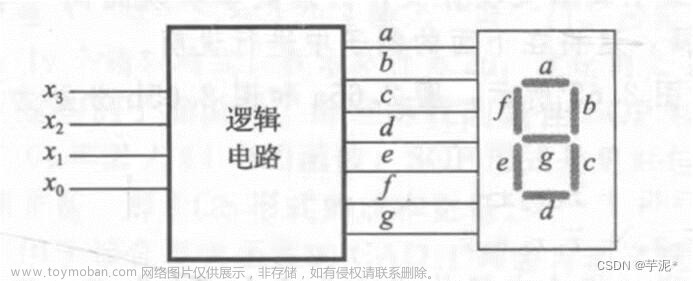

module bit3_add(operand1,operand2,cin,result,cout,DIG,seg);

input [2:0]operand1; // 加数1

input [2:0]operand2; // 加数2

input cin; // 进位输入

output [2:0]result; // 当前位输出,修改为四位

output cout; // 进位

wire [1:0] c; // 第 i 位的进位输入

wire c1; // 中间变量

bit_add a0(operand1[0],operand2[0],cin,result[0],c[0]);

bit_add a1(operand1[1],operand2[1],c[0],result[1],c1); // 将cout输出赋给c1

bit_add a2(operand1[2],operand2[2],c1,result[2],cout); // 将c1作为cin输入

output [5:0]DIG;

output reg [7:0]seg;

assign DIG[5] =1;

assign DIG[4] =1;

assign DIG[3] =1;

assign DIG[2] =1;

assign DIG[1] =1;

assign DIG[0] =0;

reg [2:0]N;

initial N =3'b0;

always @(operand1 or operand2) // operand1或operand2变化时触发

if(operand1 >= operand2) N = operand1;

else N = operand2;

reg [2:0]M;

initial M =3'b0;

always @(operand1 or operand2)

if(operand1 >= operand2) M = operand1;

else M = operand2;

always@(seg,result,result[2],result[1],result[0])

begin case({cout,result})

4'd0:seg=8'b11111100;

4'd1:seg=8'b01100000;

4'd2:seg=8'b11011010;

4'd3:seg=8'b11110010;

4'd4:seg=8'b01100110;

4'd5:seg=8'b10110110;

4'd6:seg=8'b10111110;

4'd7:seg=8'b11100000;

4'd8:seg=8'b11111110;

4'd9:seg=8'b11110110;

4'd10:seg=8'b11111101;

4'd11:seg=8'b01100001;

4'd12:seg=8'b11011011;

4'd13:seg=8'b11110011;

4'd14:seg=8'b01100111;

4'd15:seg=8'b00000000;

default:seg=8'b11111111;

endcase

end

endmodule

RTL分析图如下:

IO口分配:

由此可以实现通过用7个键位(operand1,operand2,cin)来控制输入,用LED灯的亮(1)暗(0)和十进制数码管来表示输出结果。

实例演示:

输入为111和111时,数码管显示.4(原因是只设计了一位数码管显示)

4.三位减法器(bit3_sub)

三位减法器的原理是利用位减法器(bit_sub)来实现三位减法逻辑。三位减法器将两个三位二进制数的每一位和对应的借位输入分别送入位减法器,得到每一位的差和借位输出。三位减法器的最高位的借位输出就是整个三位减法器的借位输出。

三位减法器(bit3_sub)是一个可以对两个三位二进制数和一个借位输入进行减法运算的模块,它有25个端口,分别是operand1、operand2、cin、result、cout、DIG和seg。operand1是被减数,operand2是减数,cin是借位输入,result是三位差,cout是借位输出,DIG和seg用于数码管显示。

三位减法器的代码如下:

module bit3_sub(operand1,operand2,cin,result,cout,DIG,seg);

input [2:0]operand1; // 被减数

input [2:0]operand2; // 减数

input cin; // 借位输入

output [2:0]result; // 当前位输出

output cout; // 借位

wire [1:0] c; // 第 i 位的借位输入

wire c1; // 中间变量

bit_sub a0(operand1[0],operand2[0],cin,result[0],c[0]);

bit_sub a1(operand1[1],operand2[1],c[0],result[1],c1); // 将cout输出赋给c1

bit_sub a2(operand1[2],operand2[2],c1,result[2],cout); // 将c1作为cin输入

output [5:0]DIG;

output reg [7:0]seg;

assign DIG[5] =1;

assign DIG[4] =1;

assign DIG[3] =1;

assign DIG[2] =1;

assign DIG[1] =1;

assign DIG[0] =0;

reg [2:0]N;

initial N =3'b0;

always @(operand1 or operand2) //operand1或operand2变化时触发

if(operand1 >= operand2) N = operand1;

else N = operand2;

reg [2:0]M;

initial M =3'b0;

always @(operand1 or operand2)

if(operand1 >= operand2) M = operand1;

else M = operand2;

always@(seg,result,result[2],result[1],result[0])

begin case({cout,result})

4'd0:seg=8'b11111100;

4'd1:seg=8'b01100000;

4'd2:seg=8'b11011010;

4'd3:seg=8'b11110010;

4'd4:seg=8'b01100110;

4'd5:seg=8'b10110110;

4'd6:seg=8'b10111110;

4'd7:seg=8'b11100000;

4'd8:seg=8'b11111110;

4'd9:seg=8'b11110110;

4'd10:seg=8'b11111101;

4'd11:seg=8'b01100001;

4'd12:seg=8'b11011011;

4'd13:seg=8'b11110011;

4'd14:seg=8'b01100111;

4'd15:seg=8'b00000000;

default:seg=8'b11111111;

endcase

end

endmodule

RTL分析图如下:

IO口分配:

由此可以实现通过用7个键位(operand1,operand2,cin)来控制输入,用LED灯的亮(1)暗(0)和数码管显示十进制数来表示输出结果。

实例演示:

|

| 输入为000和000时,数码管显示0 |

|

| 输入为111和000,数码管显示7 |

|

| 输入为000和111,数码管显示9 原因由于溢出,0000-0111=0000+1001=1001 |

三、分析

本报告使用Verilog语言编写了一个位加法器(bit_add)和一个位减法器(bit_sub),并将它们组合成一个三位加法器(bit3_add)和一个三位减法器(bit3_sub)。

这些模块的优点有:

1.可以用来实现更高位的加法器和减法器,只需将它们按照位数扩展即可。

2.可以用来实现更高级的运算,例如乘法、除法、移位等,只需将它们作为基本的运算单元即可。

3.可以用Verilog语言的特性,例如模块化、层次化、并发性、可综合性等,来进行设计和模拟,提高了开发的效率和灵活性。

这些模块的缺点有:

1.运算速度受到进位或借位的影响,每一位的运算都要等待前一位的进位或借位,导致了延迟和效率的降低。

2.运算精度受到位数的限制,如果运算的结果超过了位数的范围,就会产生溢出的错误,导致了结果的不准确和不可靠。

四、 结论

1.Verilog语言是一种适合用来描述和模拟数字电路的硬件描述语言,它有许多特性,例如模块化、层次化、并发性、可综合性等,使得它可以用来设计复杂的数字系统。

2.加法器和减法器是数字电路中的基本组件,它们可以对二进制数进行算术运算。本报告使用Verilog语言编写了一个位加法器(bit_add)和一个位减法器(bit_sub),并将它们组合成一个三位加法器(bit3_add)和一个三位减法器(bit3_sub)。

3.这些模块的优点是它们可以用来实现更高位的加法器和减法器,以及更高级的运算,而且可以利用Verilog语言的特性来进行设计和模拟,提高了开发的效率和灵活性。

4.这些模块的缺点是它们的运算速度受到进位或借位的影响,而且它们的运算精度受到位数的限制,如果运算的结果超过了位数的范围,就会产生溢出的错误。

——本报告由电子科技大学 李发瑞同学撰写文章来源:https://www.toymoban.com/news/detail-761556.html

多多点赞,多多支持,有不足之处请各位读者指出文章来源地址https://www.toymoban.com/news/detail-761556.html

到了这里,关于[FPGA]用Verilog写一个简单三位二进制加法器和减法器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!