【FPGA异步时钟域约束方法】——Vivado时钟组约束

在 FPGA 设计过程中,由于存在多时钟域的情况,需要采取一定的策略来处理时序约束问题。其中,异步时钟域是一种常见的设计需求,为了保证设计时序的正确性和稳定性,我们需要使用 Vivado 提供的时钟组约束方法来对异步时钟域进行约束。

-

创建时钟组

首先,在 Vivado 中选择工具栏上的“时钟组”按钮,进入时钟组设置窗口。按照要求填写时钟名称、时钟路径等信息,然后添加异步从属关系以及时钟偏差限制等约束条件。在完成设置后,单击“确定”按钮保存时钟组设置。 -

编写约束文件

在 Vivado 中创建约束文件(.xdc文件),并在文件中添加时钟组的约束语句。例如:

create_clock -name “CLK1” -period 20.0 [get_ports {CLK1}]

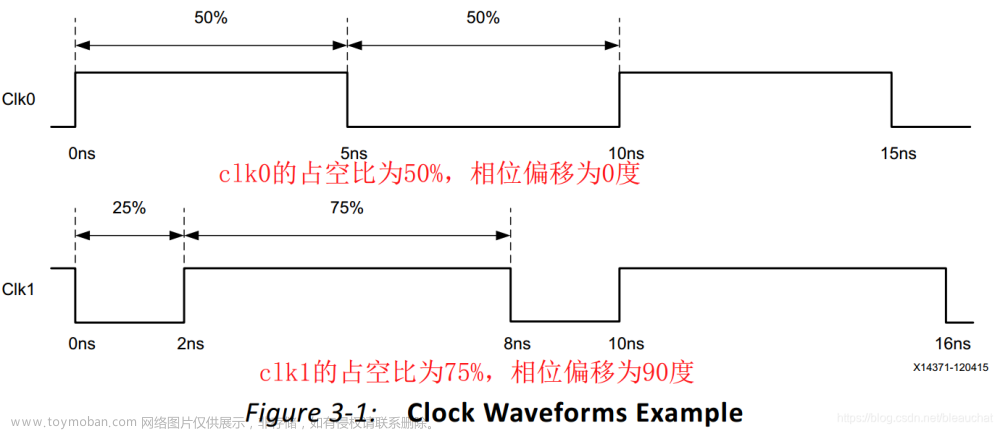

create_clock -name “CLK2” -period 10.0 -waveform {0 5} [get_ports {CLK2}]

set_input_jitter -rise_from {2.0 3.0} -fall_from {3.0 4.0} [get_ports {DATA_IN}]

set_output_delay -clock CLK1 -max 5.0 [get_ports {DATA_OUT}]

以上约束语句设置了时钟 CLK1 和 CLK2 的时钟周期分别为 20ns 和 10ns,同时 CLK2 的时钟信号采用了自定义波形。另外,还设置了该设计中输入信号 DATA_IN 的上升沿和下降沿到达时刻的抖动范围以及输出信号 DATA_OUT 相对于 CLK1 时钟的最大延迟时间。文章来源:https://www.toymoban.com/news/detail-761706.html

- 验证约束结果

在完成约束文件编写后,可以进行验证以确保时序约束的正确性。可以利用 Vivado 提供的时序分析工具来验证时序,通过约束文件中设置的时钟频率和延迟时间等参数,保证异步时钟域的同步和时序准确性。

总而言之,采取适当的时钟组约束方法可以帮助 FPGA 设计者解决异步时钟域的时序问题,提高设计的稳定性和可靠性。Vivado 提供了一套完善的工具和方法,使得我们能够更加轻松地完成 FPGA 设计任务。文章来源地址https://www.toymoban.com/news/detail-761706.html

到了这里,关于【FPGA异步时钟域约束方法】——Vivado时钟组约束的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Vivado Error问题之[DRC NSTD-1][DRC UCIO-1] FPGA管脚约束问题导致生成bit时报错,如何在不重新Implentation情况下生成bit?](https://imgs.yssmx.com/Uploads/2024/01/804972-1.png)