请阅读【嵌入式开发学习必备专栏 之Cortex-M33 专栏】

SAU NSC 介绍

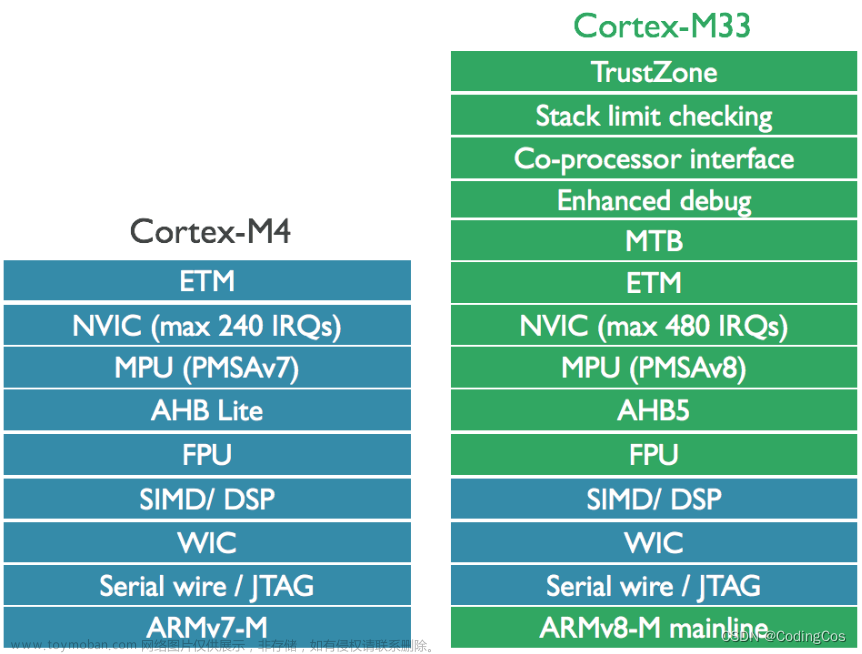

ARMv8-M 架构引入了 TrustZone 技术,它提供了一种机制来实现在单个处理器内部的安全隔离。这项技术定义了两种状态:安全状态(Secure state)和非安全状态(Non-secure state)。在此架构下,可以同时运行安全和非安全代码,并且通过硬件保护确保两者之间的隔离。

为了允许非安全代码安全地调用安全函数而不会破坏系统的安全性,ARMv8-M 引入了一种特殊的机制,即 非安全可调用(Non-secure Callable, NSC)区域。以下是一些详细解释:

安全状态(Secure state)

- 安全状态下的代码能够访问所有资源,包括安全和非安全内存以及外设。

- 任何要执行的安全代码都必须首先经过认证,并且通常被用来处理敏感数据和执行安全相关的任务。

- 安全状态下可以执行任务,如加密操作、安全启动、安全存储等。

非安全状态(Non-secure state)

- 非安全状态下的代码不能直接访问安全资源。

- 这被用来运行较少敏感的或者第三方的应用代码。

非安全可调用(Non-secure Callable, NSC)区域

如果实施了安全扩展,则 4GB 内存空间将划分为安全和非安全内存区域。安全内存空间进一步分为两种类型:

- 安全(S);

- 非安全可调用(NSC: Non-secure Callable)。

NSC 介绍

- NSC 区域是安全内存中的一个特殊区域,安全世界可以将其配置为允许非安全世界的代码进行限制性调用,这种类型的内存是 Armv8-M 处理器允许保存 SG 指令的一种内存,使软件能够从非安全状态转换为安全状态。

- 这些区域通常包含一些入口点,比如封装了安全函数的跳转指令。比如,通常 NSC 内存区域包含小型分支跳转(entry points)的表。 为了防止非安全应用程序分支到无效入口点,这里有Secure Gateway (SG) 指令。。

- 当非安全代码试图调用安全函数时,它会跳转到 NSC 区域中的入口点,然后由这个入口点安全地转发到真正的安全函数。

通过将 SG 指令的功能限制在 NSC 内存中,安全软件创建者无需在正常安全内存中意外包含 SG 指令或数据共享编码值,包含 NSC 内存位置。

当非安全程序调用安全端的函数时:

- API 中的第一条指令必须是 SG 指令。

- SG 指令必须位于由 安全属性单元 (SAU :Security Attribution Unit) 或实施定义的属性单元 ( IDAU : Implementation Defined Attribution Unit) 定义的 NSC 区域中。

引入NSC内存的原因是为了防止其他二进制数据,例如查找表,其值与SG指令的操作码相同,作为进入安全状态的入口函数。 通过分离 NSC 和 Secure 内存类型,包含二进制数据的 Secure 程序代码可以安全地放置在 Secure 区域中,而无需直接暴露于 Normal 世界,并且只能使用 NSC 内存中的有效入口点进行访问。

配置 NSC

配置 NSC 区域通常涉及设置内存保护单元(MPU)或安全属性单元(SAU)的相关区域,使其具有 NSC 属性。这通常在系统启动时,由安全世界的启动代码完成。

NSC 区域中的函数通常会使用 BXNS 指令来返回到非安全状态,确保返回时正确地恢复非安全状态的上下文。 在设计安全系统时,正确配置和使用 NSC 区域是保护系统免受未授权访问和潜在漏洞影响的关键部分。文章来源:https://www.toymoban.com/news/detail-762229.html

推荐阅读:

https://blog.csdn.net/weixin_42135087/article/details/122391507文章来源地址https://www.toymoban.com/news/detail-762229.html

到了这里,关于【ARMv8M Cortex-M33 系列 1.1 -- SAU Non-secure Callable(NSC) 介绍 】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!