[Vivado下载bit文件后不能在线捕获FPGA波形] - 解决方案详解

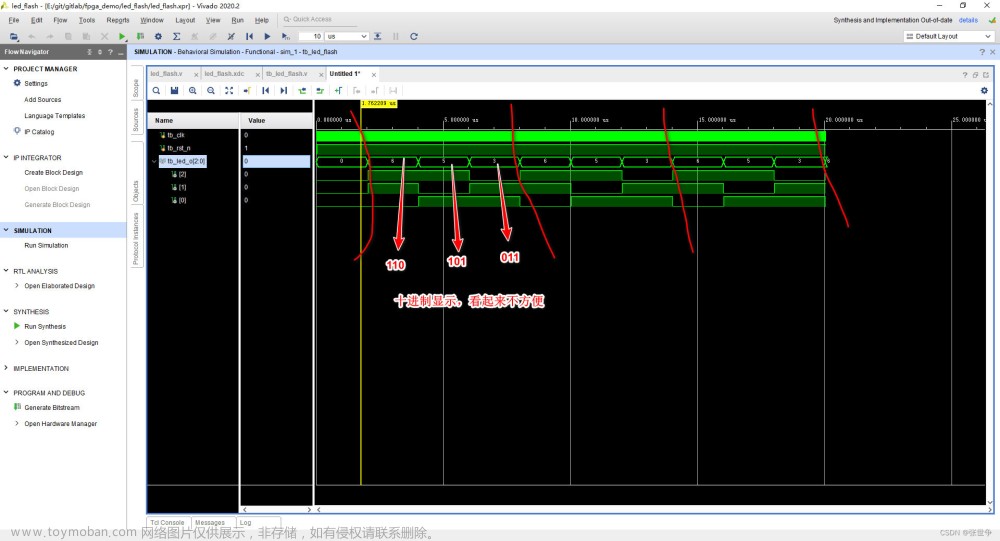

对于使用 FPGA 进行开发的工程师来说,Vivado 下载 bit 文件并在线捕获波形是一项非常基本的技能。然而,有时在下载 bit 文件之后,我们却无法在线捕获波形。这个问题可能会导致我们无法深入调试硬件问题。本文将详细介绍此问题的原因和解决方法。

问题描述

在使用 Vivado 下载 bit 文件后,通过 Hardware Manager 打开硬件管理窗口,可以看到 “Programmed” 字段下的芯片状态为 “Done”。如果我们点击 “Open Hardware Manager Target” 并尝试捕获波形,你会发现无法成功,而在 “Status” 状态下会出现以下错误:

ERROR: [Labtools 27-2269] No devices detected on target localhost:3121/xilinx_tcf/Digilent/210249A4A4C0Connection failed.Error during heartbeat transaction: Unexpected reset sequence detected

原因分析

造成这个错误的原因有很多,包括硬件连接问题、Xilinx Tools 问题、操作系统问题等等。然而,在本文中,我们要讨论的是一个比较常见且容易被忽略的原因——未正确设置 Debug Configuration。

解决方案

首先,我们需要检查我们的 Debug Configuration 是否被正确配置了。在 Vivado 的 Tcl Console 中输入以下命令:

connect_hw_server -url <连接地址>文章来源:https://www.toymoban.com/news/detail-762321.html

此处的 <文章来源地址https://www.toymoban.com/news/detail-762321.html

到了这里,关于[Vivado下载bit文件后不能在线捕获FPGA波形] - 解决方案详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![Vivado Error问题之[DRC NSTD-1][DRC UCIO-1] FPGA管脚约束问题导致生成bit时报错,如何在不重新Implentation情况下生成bit?](https://imgs.yssmx.com/Uploads/2024/01/804972-1.png)