(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

上节课的IIR设计用到了定点数的乘法,直接用的是xilinx乘法器IP核。那我们自己可不可以设计出来乘法器呢?当然是可以的,乘法器的设计也有很多的方法,我们从最简单的开始设计。

FPGA要处理的数据可以分为无符号数和有符号数,我们先从无符号数说起。假如两个无符号的数相乘,应该如何求出来结果?

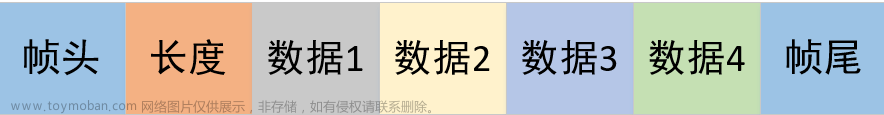

这儿就要回忆一下我们小学学习乘法的时候是如何列竖式计算求解的啦,如下两个4位的数相乘,我们会有数据Y的每1位分别和X相乘,每相乘1次X向左移动1位。最后将4个乘完的结果加起来得到最终的结果。

其实FPGA实现乘法比我们的竖式计算要简单,因为我们列的竖式计算一般都是10进制的计算,比如y3是8,x3是7,还是有一步10以内的乘法运算。而在FPGA中,数据是用2进制表示的,每一位只能是0或者1,根本不存在乘法!如果y1是0,那y1*(x3_x2_x1_x0_0)的结果就是0,如果y2是1,那y2*(x3_x2_x1_x0_0_0)的结果就是x3_x2_x1_x0_0_0,所以根本没有任何的乘法运算!

两个数相乘,如果位数分别是n和m,那最大值就是2^n*2^m,就是结果的位宽是n+m,所以在设计乘法器的时候一定要考虑位数的扩展,不然很容易出现溢出造成结果错误。

下面我们先进行无符号乘法器的设计,假设数据的位宽都是8位。首先进行了输入输出和中间信号的定义,由于输入的数据都是8位的,那输出就是8+8=16位,先扩展数据位。

先用组合逻辑实现了最终要加起来的8个数,根据din1的每1位来确定加数是din0移位扩展后的数据还是0。

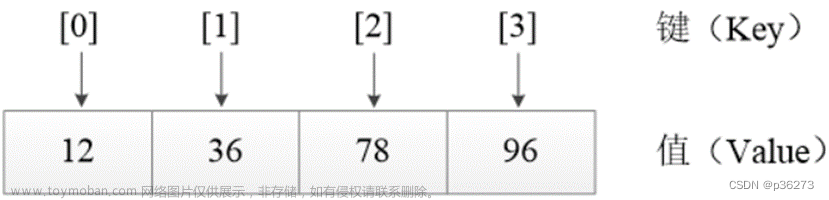

定义了一个计数器cnt,用于控制8个加数串行相加,结果存储在sum中。

最终数据结果和标志信号即可。

在仿真文件中产生随机数,仿真看看乘法的结果是否正确。数据都用无符号整数来显示,我们验证一下结果,比如232*92=21344,198*182=36036都是和结果一致,说明功能是正确的。

其实这儿有一个问题,那就是乘法的计算至少需要8个时钟周期,如果位数增多,需要的时钟周期更多,那能不能减少乘法器的时钟周期呢?

是可以的,因为8个加数都是已知的,如果1个时钟周期完成1次加法运算,那先用4个加法器在1个时钟周期完成8个数的两两相加,得到4个结果,再用2个加法器在1个时钟周期完成4个数的两两相加,得到2个结果,最后再用1个加法器完成2个数的相加,就可以得出最终的结果,需要3个时钟周期。

那乘法器的计算时间还可以进一步缩短吗?理论是上可以缩短到一个时钟周期完成乘法的运算,就是全部使用组合逻辑来做,多消耗一些FPGA的资源而已。我们来验证一下。将FPGA的代码修改如下,全部用组合逻辑来实现。

下面来看看仿真结果,189*6=1134,192*216=41472,和仿真的结果都是一样的,说明功能也是正确的,而且立马就可以出来仿真结果!

既然用组合逻辑可以快速的得出来乘法的结果,那为什么不用组合逻辑呢?为什么一定要选择时序逻辑?很多初学者都有这样的疑问,现在笔者好好的把原因和大家说明一下。

组合逻辑在前功能仿真的时候是不消耗仿真时间的,但是不代表组合逻辑在硬件电路中信号的传输不消耗时间!组合逻辑就是由一堆的LUT搭建起来的,信号在LUT之间传输时需要时间的。对于乘法器,位数越多,LUT使用的越多,从输入到输出需要的时间就越长!假设对于一个乘法器用组合逻辑实现,从输入到输出需要8ns,我们想一个时钟周期完成乘法器的计算,那系统时钟一个周期的时间就不能小于8ns,如果考虑一些裕量,我们取10ns,那系统时钟最快是100MHz。如果用时序逻辑来实现乘法器,将大的组合逻辑分解成两个4ns的小的组合逻辑,那系统时钟一个周期的时间可以取5ns,系统时钟最快可以达到200MHz!FPGA系统的整体性能立马提升了一倍!很多初学者总是抱怨,为什么自己设计的工程在FPGA板卡上速度上不去,别人都能跑到100MHz,自己的跑到50MHz功能就不正常了!很有可能的原因就是组合逻辑太长了!

上面介绍了无符号位的乘法器设计,那有符号位的乘法器应该如何设计呢?思路很简单,把符号位提取出来,剩下的位数按照无符号位的处理方式处理即可。完成无符号位的计算后,最后加上符号位即可。但是有一点需要注意,在FPGA内部,有符号的数据是按照补码来进行运算的,所以并不是把符号位去掉剩余的数据就是就是取得绝对值,比如-58,在FPGA中用11000110来表示,如果去掉最高位1,剩余得1000110就是70,直接取值是不正确的。对负数需要先取反加1,得到0111010,才是58。乘法符号的判断大家都知道,正正得正,正负得负,负负得正,这很明显可以用异或来表示。

代码进行了稍微的更改,首先是去掉符号位数据位宽减少了。其次就是得出结果的符号位,同时将输入的数据从补码转换回去。

其它的设计与无符号乘法器基本一致,就是输出结果如果是负数还有取补码回去。

最后看看仿真的结果,-92*(-97)=8924,88*(-63)=-5544,和仿真结果是一致的,功能设计正确。文章来源:https://www.toymoban.com/news/detail-762598.html

文章来源地址https://www.toymoban.com/news/detail-762598.html

文章来源地址https://www.toymoban.com/news/detail-762598.html

到了这里,关于孩子都能学会的FPGA:第十七课——用FPGA实现定点数的乘法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!