1 digilent board file 下载地址

下载地址 : https://github.com/Digilent/vivado-boards

2 下载后

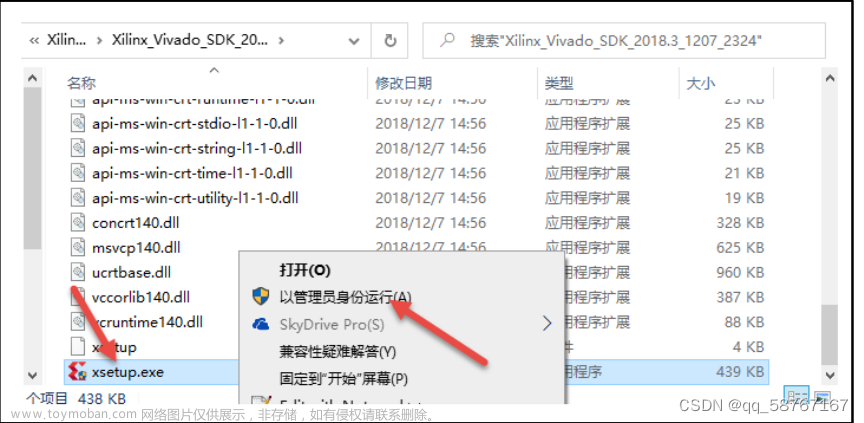

3 添加文件到 vivado 安装路径

把文件复制到

Vivado\2019.1\data\boards\board_files

文章来源:https://www.toymoban.com/news/detail-762779.html

文章来源:https://www.toymoban.com/news/detail-762779.html

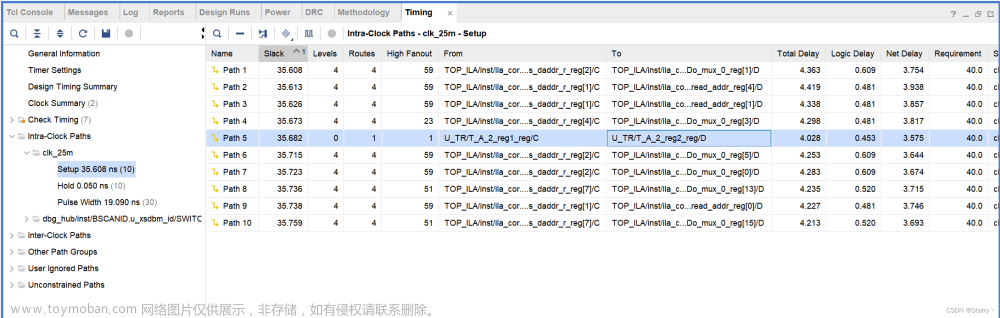

4 创建工程查看是否安装成功

文章来源地址https://www.toymoban.com/news/detail-762779.html

文章来源地址https://www.toymoban.com/news/detail-762779.html

到了这里,关于Vivado 添加FPGA开发板的Boards file的添加的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!