0x00 MUX 多路复用器(Multiplexer)

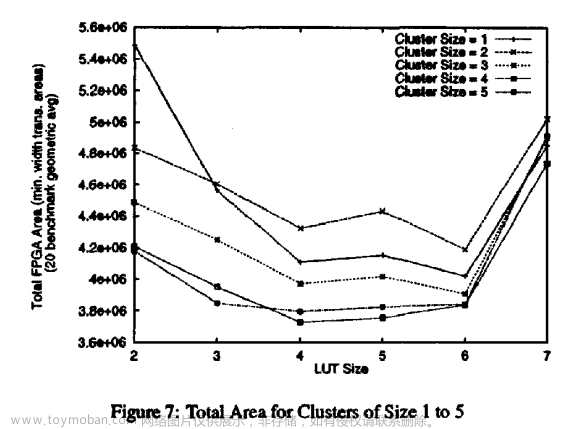

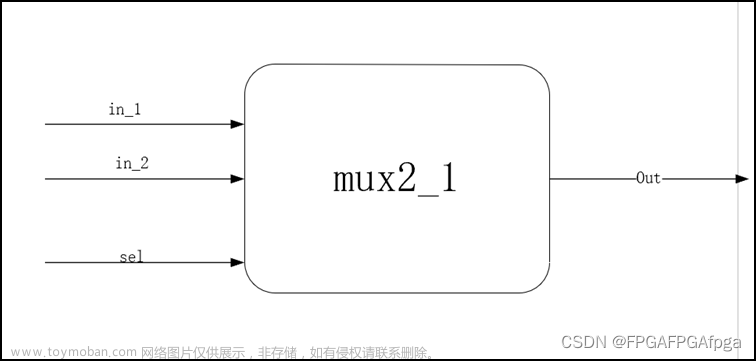

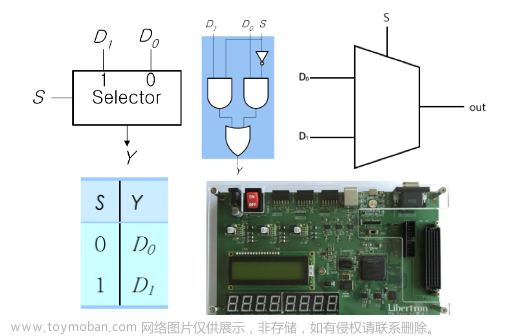

多路复用器 (Multiplexer,简称 MUX) 是一种电路,用于从多个输入中选择一个特定输入。它为 个输入提供一个输出,并有 个 select single,作用是从多个输入中选择一个。

多路复用器有两个主要部分:选择器和数据线。选择器用于选择输入信号中的一个或多个,并将其传输到输出线路上。数据线则负责传输被选择的输入信号。多路复用器的输入数量和输出数量可以根据需要而变化,常见的有 , , 等比例的多路复用器。文章来源:https://www.toymoban.com/news/detail-763237.html

多路复用器的工作原理很简单。例如,文章来源地址https://www.toymoban.com/news/detail-763237.html

到了这里,关于【FPGA】Verilog 实践:MUX 多路复用器 | Multiplexer | 实现 4 到 1 线路多路复用器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!