(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

除法是FPGA设计中的一个噩梦,主要原因就是除法器使用的时钟周期较多,拖慢了系统处理的速度。假如系统时钟是100MHz,而一个除法器需要10个时钟周期,那系统处理的最快速度也就是10MHz(先不考虑流水线操作)。所以在实际的开发中,能不用除法就不用除法,对于除数是固定数的除法,可以转变成乘法进行计算。但是很快时候,除法还是不能避免的,那本节就讲解一下除法器如何实现。

首先我们还是要回忆一下小学学习除法的时候是怎么列竖式计算的,如下所示,被除数B是1873,除数D是3,最终的商Q是1873,每一步的余数qi分别是1,8,7,3;每一步余数用R来表示。然后我们可以得到每一步的计算公式:R(i)=R(i+1)-qi*D*10^i,i=n-1,n-2,...,1。这儿还有一个比较大的问题,比如26/3这个一步,还是除法运算,用程序实现可以采用恢复余数的算法实现,就是26-3-3-3...一直减到结果是负数,然后再把3加回来,这样就可以知道减了8次3,余数是2。

如果采用二进制,可以避免上面的问题,二进制的除法公式是R(i)=R(i+1)-qi*D*2^i,i=n-1,n-2,...,1,不同与十进制的qi取值是0-9,二进制的qi取值是0和1,所以就不用考虑恢复余数的算法了,只需要判断R(i+1)和qi*D*2^i的大小关系即可!

但是用程序来实现二进制的除法还有一个问题,就是有效位的对其问题,比如被除数B是4位1111,除数D也是4位的,那可以是1111,也可以是0011,甚至是0001,如下所示,当除数D是1111的时候,商Q只有最低位时1,而当除数D是1111的时候,商Q四位全是1,但是实际工程中,不知道D的有效位是多少,那如何才能做到通用呢?

笔者使用了一种将除数先左移N-1位的方法进行计算(N是被除数的位数;之所以左移N-1,是考虑除数是1的情况),然后再依次右移动一位进行判断和计算,整个过程需要N次。也就是N个时钟周期。

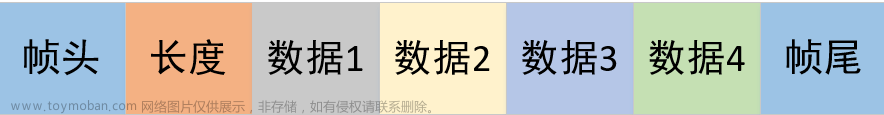

下面通过FPGA设计来验证上面方法的可行性。系统时钟100MHz,低电平复位,被除数是16位,除数是8位,都是无符号的整数,用FPGA实现除法运算,得出商和余数。

定义了相关的输入和输出,用参数定义了除法的计数器次数QUOT_CNT,因为被除数是16位,所以需要计数16次。DATA_NUM主要用来控制计数器产生结果的使能信号div_vld和锁存结果quotient和remainder。

用数组定义了每一步计算需要除数的移位值,当然也可以不用数组,在代码中直接用也可以。

计数器cnt的功能非常简单,就是控制每一步的计算和比较;remainder_tmp用于存储每一步计算的余数,当然第一步是被除数dividend,每一步判断remainder_tmp和divisor_array[cnt]的大小,来确定是执行减法还是保持余数不变。quotient_tmp用于存储每一步计算的商,先计算出来高位后计算出来低位,所以进行左移。每一步判断remainder_tmp和divisor_array[cnt]的大小来决定商到底是1还是0。

最后完成计算,产生输出结果的使能信号div_vld和锁存结果quotient和remainder。这儿稍微考虑了除数是0的情况,直接在输出做了处理。

在仿真tb文件中产生随机的被除数和除数,双击sim文件夹下的top_tb.bat文件,完成自动化的仿真。

仿真结果如下所示,随便找两个数据计算一下,33222/77商是431,余数是35;11418/182商是62,余数是134,和仿真结果是一样的,功能设计正常。如果想得到M个小数位,在被除数后补零,将除数先左移N+M-1,再右移动N+M-1步完成运算和比较即可,只需要更改几个参数,数组和位宽即可,逻辑几乎没有任何的改变。

和乘法器一样,有符号位的除法器计算的思路也是一样,先把有符号数转变成无符号数进行计算,结果再加上符号位即可。

参数稍有变化,去掉一个符号位,实际只需要计算15次即可。位宽也进行了对应修改。

数组又由16个变成了15个。

其它的代码和无符号数的除法基本一样,最终的结果加上符号位即可。

最后看看仿真结果,我们计算一下有负数的,-32314/77商是-419,余数是-51;-7180/(72)商是99,余数是52,和仿真结果是一样的,功能设计正常。文章来源:https://www.toymoban.com/news/detail-764110.html

文章来源地址https://www.toymoban.com/news/detail-764110.html

文章来源地址https://www.toymoban.com/news/detail-764110.html

到了这里,关于孩子都能学会的FPGA:第十八课——用FPGA实现定点数的除法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!