常见英文缩写

ZYNQ:是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合。

PS:(Processing System),ZYNQ可以大概分为ARM和FPGA两部分,PS就是ARM的SOC部分,是整块板子的处理系统。

PL:(Progarmmable Logic),意为可编程逻辑,也就是ZYNQ上的FPGA部分。

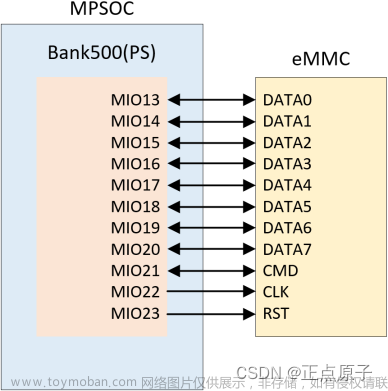

MIO:(Multiuse I/O),多功能IO引脚,如果学过单片机可以把它理解为引脚复用,属于PS部分,也就是ARM部分。值得一提的是,MIO 信号对 PL部分是不可见的,所以对 MIO 的操作可以看作是纯 PS 的操作。

EMIO:(Extendable Multiuse I/O),可拓展多功能IO引脚,依然属于PS部分,但是连接到了PL上,再从PL的引脚连到芯片外面实现数据输入输出。如果MIO不够用的话, PS 可以通过驱动 EMIO 控制 PL 部分的引脚 。EMIO 有 64 个引脚可供我们使用。

APU:(Application Processor Unit),应用处理器单元,曾经AMD公司用它来特指加速处理器(Accelerated Processing Units),但是在ZYNQ上的意思就截然不同,注意区分。APU包含了双ARM-CortexA9核,加上高速缓冲,DMA,定时器,中断控制,浮点和NEON协处理,可以类比51单片机中的MCU,Cortex-M系列的STM32上的MPU来理解。

但是APU这个称呼还是有说法的,没有了M就说明意图摆脱微处理器Micro的名头,换上Application就不简单了,说明在上面可以跑应用程序, 暗示着这个系统是需要全尺寸的操作系统的。

TTC:(Triple Time Counter),直译就是三倍时间计数器,其实是这个计数器内有3个独立通道,可以独立计数。挂在APB上,为系统或外设提供定时或计数服务的。

WDT:看门狗定时器,有两个, 分别监视ARM-Cortex A9用的。 如果软件跑飞,无法清定时器,一段时间后,看门狗就复位。一般没什么用,学STM32时就觉得这功能还挺厉害,能一直监视程序有没有跑飞,后来发现跑飞的几率太小了,现在的板子稳定性都很好,以至于我现在都没见到过看门狗起作用,不过也算是个风险保障。

SWDT:系统级看门狗定时器, 这个看门狗的时钟和复位信号,都可以来自于芯片外部, 这样,即使系统有严重故障,比如时钟频率本身都有问题了,仍然可以通过与系统无关的外部信号计数,计数满就复位。

SCU:(Snoop Control Unit),用来保持双核之间的数据Cache的一致性,两个ARM-Cortex A9,如果一个写存储时只写进缓存,没写进主存,如果第二个A9读操作,涉及到第一个写脏了的数据段, SCU要保证第二个A9的缓存里是最新的数据。 SCU的存在,才使得两个核成互相联系的“双核”,才能成为MPsoc。

ZYNQ简介

ZYNQ的本质特征,是它组合了一个双核ARMCortex-A9处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件。由于该新型器件的可编程逻辑部分基于赛灵思28nm工艺的7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的一致性,同时也方便日后本系列新产品的命名。

在过去,SoC这个术语常用于指专用集成电路(Application Specific Integrated Circuit,ASIC)。

可编程片上系统(SOPC,System-on-Progammable-Chip)为上述应用提供了一个更灵活的解决方案:一种在可编程、可重新配置的芯片上实现的SoC。其中,可编程的芯片指的就是FPGA。

相比于SOPC,ZYNQ为实现灵活的SoC提供了一个更加理想的平台:Xilinx将其打造成“全可编程片上系统(APSoC,All-ProgrammableSoC)”。它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

在ZYNQ上,ARMCortex-A9是一个应用级的处理器,能运行像Linux这样的操作系统,而可编程逻辑是基于Xilinx7系列的FPGA架构。ZYNQ架构实现了工业标准的AXI接口,在芯片的两个部分之间实现了高带宽、低延迟的连接。这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会产生在两个分立器件之间的接口开销。

ZYNQ PL简介

ZYNQ PL部分等价于 Xilinx 7系列 FPGA

简化的FPGA基本结构由6部分组成

-

可编程输入/输出单元

-

基本可编程逻辑单元

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的逻辑功能。FPGA一般是基于SRAM工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT,LookUpTable)和寄存器(Register)组成。Xilinx7系列FPGA内部查找表为6输入,查找表一般完成纯组合逻辑功能。FPGA内部寄存器结构相当灵活,可以配置为带同步/异步复位或置位,时钟使能的触发器,也可以配置成锁存器,FPGA依赖寄存器完成同步时序逻辑设计。

比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存器与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。

Altera可编程逻辑单元通常被称为LE(LogicElement),由一个寄存器加一个LUT构成。Altera大多数FPGA将10个LE有机地组合在一起,构成更大的功能单元——逻辑阵列模块(LAB,LogicArrayBlock)。LAB中除了LE还包含LE之间的进位链,LAB控制信号,局部互联线资源,LUT级联链,寄存器级联链等连线与控制资源。

Xilinx 7系列 FPGA中的可编程逻辑单元叫 CLB(Configurable Logic Block,可配置逻辑块)每个 CLB 里包含两个逻辑片(Slice)。每个 Slice由 4 个查找表、8个触发器和其他一些逻辑所组成的。

CLB是逻辑单元的最小组成部分,在PL中排列为一个二维阵列,通过可编程互联连接到其他类似的资源。每个CLB里包含两个逻辑片,并且紧邻一个开关矩阵

-

嵌入式块RAM

目前大多数FPGA都有内嵌的块RAM(BlockRAM),FPGA内部嵌入可编程RAM模块,大大地拓展了FPGA的应用范围和使用灵活性。

-

布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源。

-

底层嵌入功能单元

底层嵌入功能单元的概念比较笼统,这里我们指的是那些通用程度较高的嵌入式功能模块,比如PLL(PhaseLockedLoop)、DLL(DelayLockedLoop)、DSP、CPU等。

-

内嵌专用硬核

这里的内嵌专用硬核与前面的底层嵌入单元是有区分的,这里讲的内嵌专用硬核主要指那些通用性相对较弱,不是所有FPGA器件都包含硬核。

在ZYNQ的PL端有一个数模混合模块——XADC,它就是一个硬核。XADC包含两个模数转换器(ADC),一个模拟多路复用器,片上温度和片上电压传感器等。我们可以利用这个模块监测芯片温度和供电电压,也可以用来测量外部的模拟电压信号。

ZYNQ PL架构

ZYNQ PS简介

ZYNQ实际上是一个以处理器为核心的系统,PL只是它的一个外设。Zynq-7000系列的亮点在于它包含了完整的ARM处理器系统,且处理器系统中集成了内存控制器和大量的外设,使Cortex-A9处理器可以完全独立于可编程逻辑单元。而且实际上在ZYNQ中,PL和PS两部分的供电电路是独立的,这样PS或PL部分不被使用的话就可以被断电。

使用FPGA的可编程逻辑资源搭建的处理器我们称之为“软核”处理器,它的优势在于处理器的数量以及实现方式的灵活性。

ZYNQ中集成的是一颗“硬核”处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的优势是它可以获得相对较高的性能。另外,ZYNQ中的硬件处理器和软核处理器并不冲突,我们完全可以使用PL的逻辑资源搭建一个Microblaze软核处理器,来和ARM硬核处理器协同工作。

Zynq处理器系统里并非只有ARM处理器,还有一组相关的处理资源,形成了一个应用处理器单元(ApplicationProcessingUnit,APU),另外还有扩展外设接口、cache存储器、存储器接口、互联接口和时钟发生电路等。

ZYNQ处理器系统(PS)示意图如下所示,其中红色高亮区域为APU。

- APU

APU主要是由两个ARM处理器核组成的,每个都关联了一些可计算的单元:一个NEONTM媒体处理引擎(MediaProcessingEngine,MPE)和浮点单元(FloatingPointUnit,FPU);一个内存管理单元(MemoryManagementUnit,MMU);和一个一级cache存储器(分为指令和数据两个部分)。APU里还有一个二级cache存储器,再往下还有片上存储器(OnChipMemory,OCM),这些是两个ARM处理器共用的。最后,由一个一致性控制单元(SnoopControlUnit,SCU)在ARM核和二级cache及OCM存储器之间形成了桥连接。SCU还部分负责与PL对接,图中没有标出这个接口。

- 外部接口

Zynq PS实现了众多接口,既有PS和PL之间的,也有PS和外部部件之间的。PS和外部接口之间的通信主要是通过复用的输入/输出(MultiplexedInput/Output,MIO)实现的,它提供了可以灵活配置的54个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。当需要扩展超过54个引脚的时候可以通过**扩展MIO(ExtendedMIO,EMIO)**来实现,EMIO并不是PS和外部连接之间的直接通路,而是通过共用了PL的I/O资源来实现的。

-

存储器接口

Zynq-7000APSoC上的存储器接口单元包括一个动态存储器控制器和几个静态存储器接口模块。动态存储器控制器可以用于DDR3、DDR3L、DDR2或LPDDR2。静态存储器控制器支持一个NAND闪存接口、一个Quad-SPI闪存接口、一个并行数据总线和并行NOR闪存接口。

-

片上存储器

片上存储器包括256kB的RAM(OCM)和128kB的ROM(BootROM)。OCM支持两个64位AXI从机接口端口,一个端口专用于通过APUSCU的CPU/ACP访问,而另一个是由PS和PL内其他所有的总线主机所共享的。BootROM是ZYNQ芯片上的一块非易失性存储器,它包含了ZYNQ所支持的配置器件的驱动。BootROM对于用户是不可见的,专门保留且只用于引导的过程。

-

AXI接口

ZYNQ将高性能ARMCotex-A系列处理器与高性能FPGA在单芯片内紧密结合,为设计带来了如减小体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与FPGA融合在一个芯片上之后,片内处理器与FPGA之间的互联通路就成了ZYNQ芯片设计的重中之重。如果CotexA9与FPGA之间的数据交互成为瓶颈,那么处理器与FPGA结合的性能优势就不能发挥出来。

Xilinx从 Spartan-6和 Virtex-6系列开始使用 AXI协议来连接 IP核。在 7系列和 ZYNQ-7000 AP SoC 器件中,Xilinx在 IP核中继续使用 AXI协议。AXI的英文全称是 Advanced eXtensible Interface,即高级可 扩展接口,它是 ARM公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。文章来源:https://www.toymoban.com/news/detail-764568.html

AXI协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:文章来源地址https://www.toymoban.com/news/detail-764568.html

- 总线的地址/控制和数据通道是分离的

- 支持不对齐的数据传输

- 支持突发传输,突发传输过程中只需要首地址;

- 具有分离的读/写数据通道;

- 支持显著传输访问和乱序访问;

- 更加容易进行时序收敛。

到了这里,关于ZYNQ相关的常见概念的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!