(一)手把手教你如何通过ARM DesignStart计划在FPGA上搭建一个Cortex-M3软核

一、ARM DesignStart计划

1.1 如何下载ARM DesignStart Cortex-M3相关文件

关于ARM DesignStart计划的介绍:ARM DesignStart计划——私人定制一颗ARM处理器 - 知乎 (zhihu.com)。

在arm Developer官网[Arm Developer](https://developer.arm.com/downloads)右上方的Downloads中搜索ARM DesignStart Cortex-M3第一个即是FPGA上定制的Cortex-M3软核IP。

以下是我从官网下载的Cortex-M3的百度网盘链接,M0也是同样的方法:https://pan.baidu.com/s/1jO1cTTL89xig5wEomUTrlQ?pwd=1234。

上面我废话了两句是因为我一开始在官网主页中直接搜索ARM DesignStart Cortex-M3一直找不到软核工具包,只能找到相关的用户说明书,Cortex-M3软核IP要到Downloads才能找到。总之是我搜索方式不对的原因,给大家避个坑。

1.2 Cortex-M3 DesignStart Eval工具使用介绍

在arm Developer官网主页面中直接搜索Arm Cortex-M3 DesignStart Eval User Guide可以找到Cortex-M3软核IP的相关用户使用手册。

在该用户使用手册文件的1-17页有具体的文件结构说明。其中我们用到的我觉得比较重要的是Cortex-M3内核文件夹,在下图1.5路径中:

在cmsdk(Cortex-M System Design Kit,Cortex-M系统设计工具包)文件夹中,有着大量官方提供的现成的MCU实现组件,像串口、定时器等外设,ahb、apb总线接口,经过封装的FPGA内部sram存储器等,这些组件都是由verilog代码实现的。如下图1.7所示:

另外一个很常用的用户使用手册是Arm Cortex-M System Design Kit Technical Reference Manual,可以直接在官网主页搜索得到。这个用户手册中有很大一部分是对cmsdk工具包文件夹中的系统组件的说明,例如对上图1.7中cmsdk_apb_uart和cmsdk_apb_time这两个由verilog代码实现的外设IP的寄存器构成、时序逻辑等都在该文档中有详细说明。在我们的系统实现中,我就是对着这个文档对gpio、uart和timer这三个外设编写的软件驱动。该文档的具体内容如下图1.8所示:

如上图可以看到定时器外设的寄存器地址偏移、位宽、描述等,除此之外还有模块端口信号,特征描述等。

二、如何搭建软核

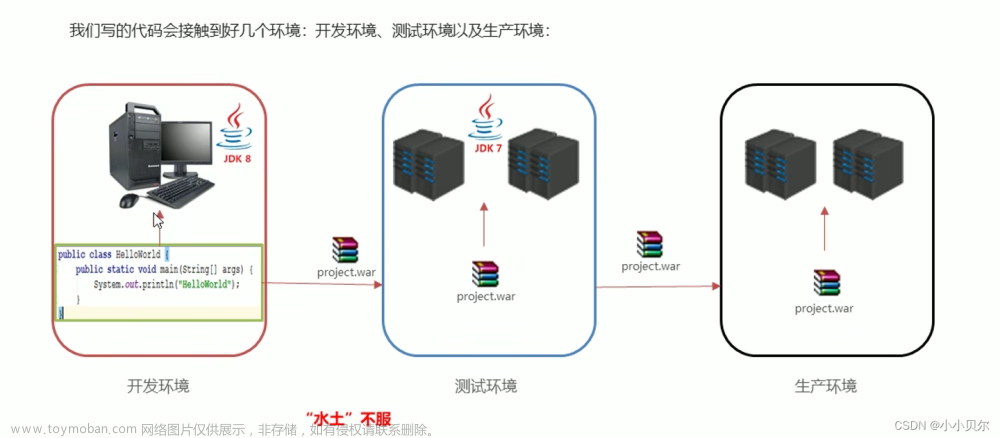

在搭建SoC系统的过程中碰到过许多问题查阅了许多资料,这里就不一一详细说明了,我把查阅过的视频和资料都列出来:

-

使用Keil设计基于ARM DesignStart M3软核的软件程序_哔哩哔哩_bilibili

该视频前半段是在VIVADO上搭建硬件资源,后半段在配置KEIL,因为我们是在安路的平台上搭建,因此跳过了前面的部分,看的是后半段的KEIL配置以及代码编写,主要是实践操作性。

-

使用CMSDK搭建CortexM3SoC - 极术社区 - 连接开发者与智能计算生态 (aijishu.com)

这篇文章可以结合着下面的极术社区的视频一起看,主要写了:

- 使用CMSDK生成总线矩阵,这部分比较复杂,主要就是给主从设备分配端口和地址,具体怎么操作我不太懂是我队友做的。

- 硬件上添加CMSDK APB外设,文中以uart为例如何将外设模块端口信号和APB总线相连,连接至AHB总线上也大同小异。

- 自定义外设,简要地讲解了如何编写外设硬件代码和完成外设软件驱动。

- 最后给出了一份硬件和软件上的参考范例。

-

极术公开课|【集创赛培训】基于Arm Cortex M3的SoC设计与FPGA实现_哔哩哔哩_bilibili

这是往年集创赛ARM杯的培训视频,很有必要看一遍,看完之后可以对整个软核的搭建有一个清晰的概念,主要偏向理论性并给出整体框架概念。

-

GitHub - ian-lab/my_CortexM3

一个开源GitHub项目,是一个完整的Cortex-M3的SoC系统范例。

-

目录 - Arm Cortex-M0的SoC实现 (yuque.com)

硬木课堂知识库,其中一个章节就是Arm Cortex-M0的SoC实现,基于安路EG4S20。这几篇文章兼有理论和实践,理论上如总线的知识、SoC的组成等,对在大脑中构建一个整体SoC概念很有帮助。实践上这篇文章手把手教你硬件代码如何编写,KEIL上如何配置等等。但是因为这篇文章是用汇编语言进行软件编写的,因此在我比赛过程中就没有参考。另外这些文章中提到的下载的文件都没有,不用找和问了。

三、总体架构

3.1 整体架构展示

本系统的系统框图如图3.1。在基于ARM DesignStart计划开放的Eval版ARM Cortex-M3软核搭建片上系统,硬件主要模块包括(图中的ACC硬件加速器实际上还没有):

- ARM Cortex-M3处理器内核;

- 一、二级AHB系统总线和二级APB系统总线;

- 总线间接口和总线与外设间接口;

- 挂载在AHB和APB总线上的外设:

- 由FPGA片上BRAM实现的程序和数据存储器ITCM和DTCM;

- 片上功能外设,包括串口UART,GPIO,定时器TIMER,外部SDRAM,FLASH;

- SWD调试接口;

- 外部SDRAM与总线之间的高速缓存Cache。

以上系统框图以及顶层代码的排布都是按照系统地址递增的顺序排列的,为的是能有更清晰的逻辑,下面是整个系统的地址层次。

Cortex-M3的总线位宽为32位,因此提供了4GB的存储器寻址空间。在我们设计的片上SOC中,具有片内RAM,片外SDRAM和外设驱动层电路,因此具有灵活的地址映射和寻址方式。具体的地址空间映射如下图3.2所示:

文章来源:https://www.toymoban.com/news/detail-764613.html

文章来源:https://www.toymoban.com/news/detail-764613.html

3.2 顶层文件代码分析

我们的所有工程都会上传到我的github仓库,后期也会不断做修改:JimmyForest · GitHub。以下是我对着顶层文件进行的代码分析,简单讲述了搭建软核的思路以及软核的框架结构:文章来源地址https://www.toymoban.com/news/detail-764613.html

- 最开始的一个GLOBAL BUF(这个在我们的代码的注释中,以下的都是)是对全局时钟走线的处理,走全局时钟网络的信号具有低偏斜、低抖动以及高扇出的特点。

- 接下来是DEBUG IOBUF对调试接口的三态处理,因为安路中找不到相应的三态原语,因此就用了

1'bz代替。 - 后面两个是全局复位的处理。

- 接下来的

cortexm3ds_logic模块是官方提供的Cortex-M3内核,即图3.1中的Cortex-M3 Core,为整个系统的中央CPU。该模块的底层代码由大量的assign语句构成,且所有信号均由无规律的字母和数字组成无实际含义,因此具有很差的可读性。另外该内核主要有三大主机接口与一级AHB总线相连接,分别是I_bus(Instructions)指令总线,D_bus(Data)数据总线和SYSTEM_bus系统总线。前两个分别是内核与ITCM和DTCM交互分别取指和数据读写,系统总线还不是很懂,CSDN上有说法是这条总线用来加载外设。 - 在内核模块的后面是一级AHB稀疏总线矩阵

L1AhbMtx,这是AHB总线的核心部分。该模块包含多个子模块,其中包括多个仲裁器、地址译码器、从机的输入级和主机的输出级模块(后面两个什么意思和功能我不懂,是根据注释翻译的)。相比于后面的二级AHB总线模块这是一个完整的总线模块,拥有总线的完整功能,可以通过在第二点中2、3两小点中提供文章和视频提供的方法进行生成。 - 在一级AHB总线矩阵模块下面的是

ahb_eram,此处的eram也即可理解为BRAM即为块状(BLOCK)RAM,利用大块的RAM作为ITCM指令存储空间。之前采用分布式SRAM作为ITCM的存储空间导致存储资源不够是因为SRAM的本质是LUT查找表,LUT较适合用于小容量的存储和逻辑电路的综合,对于大容量的存储使用SRAM效率十分低下。 - 在ITCM下面的是

cmsdk_ahb_to_sram,这个并不是DTCM存储器SRAM,而是AHB总线和DTCM的接口层。下面的cmsdk_fpga_sram才是DTCM的SRAM实例化模块。这里采用分布式SRAM是因为在KEIL中配置ITCM和DTCM时。ITCM大小为64kb bit,DTCM大小为16kb bit。因此DTCM大小较小采用了分布式RAM实现。 - 接下来的是APB总线部分,首先是APB与AHB的接口模块

cmsdk_ahb_to_apb。后面是APB总线的核心部分cmsdk_apb_slave_mux,根据名字看mux是多路选择器,但模块内部不仅包含了从机多路选择器还包含了地址译码器。因为APB总线是单主机结构因此不存在仲裁器。具体的总线内容放到下一篇文章。 - 再下面是两个挂载在APB总线上的外设,串口和定时器。前面APB总线的地址译码器决定了两个外设的基地址。

- 在APB后面的是二级AHB总线,和APB总线一样,AHB与AHB总线之间有一个同步桥模块

cmsdk_ahb_to_ahb_sync,是一级AHB总线和二级AHB总线之间的数据指令同步接口模块。 - 在同步桥下面是

AHBlite_Interconnect,AHBlite是只AHB总线的简化版本,AHB支持多主机而AHBlite仅支持单主机,因此AHBlite在AHB总线的基础上可以简化仲裁器等大量的控制信号。例如在该系统中一级AHB总线是二级AHB总线的主机,在二级AHB总线下可以挂载多个外设。AHB的AHBlite_Interconnect模块和APB的cmsdk_apb_slave_mux一样也是由地址译码器和多路选择器组成。 - 在二级AHB总线下面是三个挂载在总线上的外设GPIO、LCD和FLASH。最后在一级AHB总线上单独挂载了一个外设外部SDRAM,不挂载在二级AHB总线上是为了提高外部SDRAM的数据读写效率。数据经过总线的读写会造成时钟延迟降低数据的传输效率。

- 在顶层文件的代码最后一行一个

assign语句是系统中断,IRQ信号的位宽大小为240表示该系统最大可以支持240个自定义的外部中断。如在该系统中就有定时器中断,GPIO1的中断等等。

到了这里,关于(一)手把手教你如何通过ARM DesignStart计划在FPGA上搭建一个Cortex-M3软核的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[R语言]手把手教你如何绘图(万字)](https://imgs.yssmx.com/Uploads/2024/02/441311-1.png)