目录

1.算法仿真效果

2.算法涉及理论知识概要

2.1、桶形移位寄存器的基本原理

2.2、桶形移位寄存器的数学模型

2.3、桶形移位寄存器的实现步骤

3.Verilog核心程序

4.完整算法代码文件

1.算法仿真效果

本系统进行了两个平台的开发,分别是:

Vivado2019.2

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition

其中Vivado2019.2仿真结果如下:

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

2.算法涉及理论知识概要

桶形移位寄存器(Linear Feedback Shift Register,LFSR)是一种在数字电路、通信以及密码学中广泛应用的技术。其基本原理是通过移位寄存器中的位运算来生成一个伪随机序列。桶形移位寄存器具有体积小、速度快、易于实现以及循环性好等优点,因此被广泛应用于通信系统中的编码、加密等领域。

2.1、桶形移位寄存器的基本原理

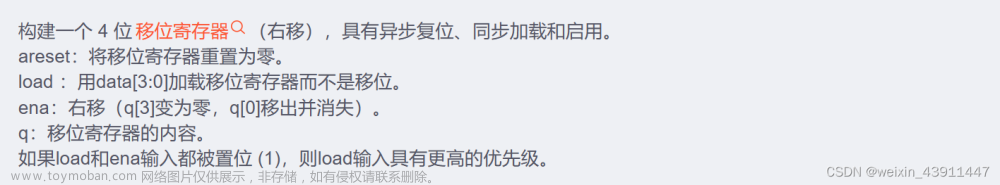

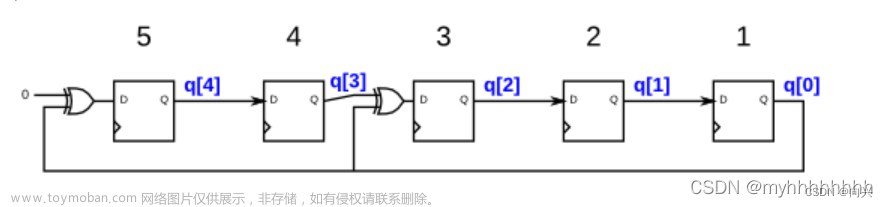

桶形移位寄存器是一种寄存器,其结构如图1所示。其中,$D$个触发器通过互相反馈的方式组成一个环形结构,称为反馈路径。每个触发器的输出连接一个异或门,其中一个输入为其输入,另一个输入为反馈路径上的某些输出的异或和。桶形移位寄存器通过对输入比特进行移位和反馈比特运算,可以在寄存器中生成一个伪随机序列。

桶形移位寄存器的输出序列可以表示为:

$$

s_n=s_{n-D}\oplus s_{n-T_1}\oplus \cdots \oplus s_{n-T_d}

$$

其中,s_n表示第n个时刻的输出比特,D表示移位寄存器的长度,T_1,\cdots,T_d表示反馈路径上的比特位置,\oplus表示异或运算。

桶形移位寄存器的输出序列具有循环性,其周期为2^D-1。当移位寄存器中所有的触发器都处于1的状态时,输出序列为0。因此,桶形移位寄存器中的比特数需要选择为质数,以避免出现所有触发器处于1的情况。

2.2、桶形移位寄存器的数学模型

桶形移位寄存器的输出序列可以表示为一个线性反馈移位寄存器方程:

$$

s_n=\sum_{i=0}^{D-1}c_is_{n-i}

$$

其中,c_i表示反馈路径上的系数,s_{n-i}表示第n-i个时刻的输出比特。

将线性反馈移位寄存器方程表示为矩阵形式:

$$

\begin{bmatrix}

s_n\

s_{n-1}\

\vdots\

s_{n-D+1}

\end{bmatrix}=

\begin{bmatrix}

c_0 & c_1 & \cdots & c_{D-1}\

1 & 0 & \cdots & 0\

\vdots & \vdots & \ddots & \vdots\

0 & 0 & \cdots & 1

\end{bmatrix}

\begin{bmatrix}

s_{n-1}\

s_{n-2}\

\vdots\

s_{n-D}

\end{bmatrix}

$$

其中,第一行表示当前时刻的输出比特,第二行到第D行表示过去D-1个时刻的输出比特。因此,线性反馈移位寄存器可以表示为一个$(D\times D)$的矩阵。

桶形移位寄存器的输出序列也可以表示为一个多项式:

$$

S(x)=c_0+c_1x+\cdots+c_{D-1}x^{D-1}

$$

其中,x表示多项式中的变量。通过多项式的乘法和取模运算,可以实现桶形移位寄存器的移位和反馈运算。具体地,设当前时刻的输出序列为s_n,则移位和反馈运算可以表示为:

$$

s_n=x\cdot s_{n-1}\bmod S(x)

$$

其中,\bmod表示取模运算,S(x)表示桶形移位寄存器的多项式表示。

2.3、桶形移位寄存器的实现步骤

桶形移位寄存器的实现步骤如下:

选择一个合适的多项式S(x),并确定移位寄存器的长度$D$和反馈路径上的比特位置T_1,\cdots,T_d。

初始化移位寄存器的状态,将所有触发器的初始值设为0或1。

对于每个时刻,执行移位和反馈运算,生成输出序列s_n。

重复步骤3,直到生成所需长度的输出序列。

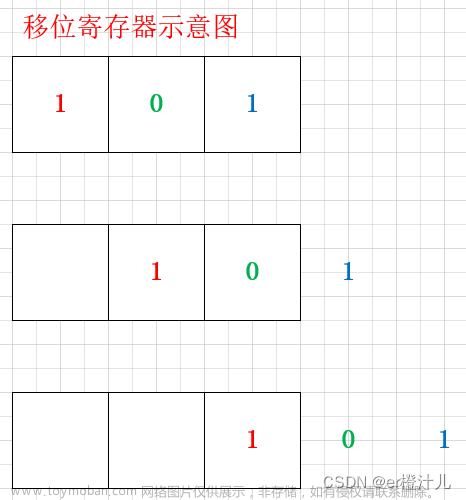

下面给出一个示例,演示如何实现一个长度为4的桶形移位寄存器,其多项式为$S(x)=x^4+x+1$,反馈路径上的比特位置为$T_1=4$和$T_2=3$。

首先,将多项式$S(x)$转化为二进制表示:

$$

S(x)=x^4+x+1=10101

$$

初始化移位寄存器的状态,假设初始值为$s_0=1101$。

对于每个时刻,执行移位和反馈运算。假设当前时刻为$n=1$,执行如下操作:

3.1. 将寄存器向左移动一位,将最高位舍弃,将当前时刻的输入比特(可以是0或1)插入到最低位。

$$

s_1=1011

$$

3.2. 计算反馈路径上的比特的异或和,并将其作为当前时刻的输出比特。

$$

s_1=s_0\oplus s_{0-T_1}\oplus s_{0-T_2}=1\oplus 0\oplus 1=0

$$

重复步骤3,直到生成所需长度的输出序列。假设需要生成10个比特的输出序列,则输出序列为:

$$

0\ 1\ 1\ 0\ 1\ 0\ 0\ 1\ 1\ 1

$$

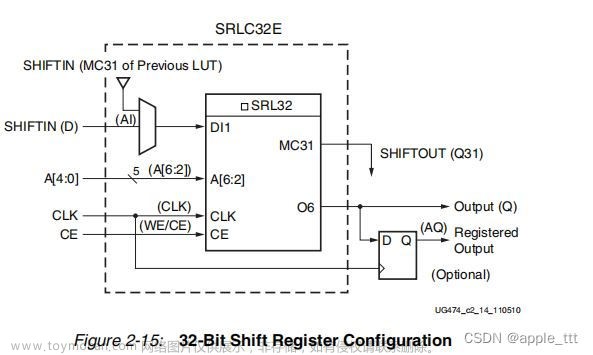

桶形移位寄存器是一种在数字电路、通信以及密码学中广泛应用的技术。其基本原理是通过移位寄存器中的位运算来生成一个伪随机序列。桶形移位寄存器具有体积小、速度快、易于实现以及循环性好等优点,因此被广泛应用于通信系统中的编码、加密等领域。本文从数学原理和实现步骤两个方面,详细介绍了桶形移位寄存器的基本原理、结构、数学模型以及实现步骤。文章来源:https://www.toymoban.com/news/detail-764988.html

3.Verilog核心程序

always@(*)

begin

case(sn_temp)

0:dout_temp = dat_temp[63:31];

1:dout_temp = dat_temp[62:30];

2:dout_temp = dat_temp[61:29];

3:dout_temp = dat_temp[60:28];

4:dout_temp = dat_temp[59:27];

5:dout_temp = dat_temp[58:26];

6:dout_temp = dat_temp[57:25];

7:dout_temp = dat_temp[56:24];

8:dout_temp = dat_temp[55:23];

9:dout_temp = dat_temp[54:22];

10:dout_temp = dat_temp[53:21];

11:dout_temp = dat_temp[52:20];

12:dout_temp = dat_temp[51:19];

13:dout_temp = dat_temp[50:18];

14:dout_temp = dat_temp[49:17];

15:dout_temp = dat_temp[48:16];

16:dout_temp = dat_temp[47:15];

17:dout_temp = dat_temp[46:14];

18:dout_temp = dat_temp[45:13];

19:dout_temp = dat_temp[44:12];

20:dout_temp = dat_temp[43:11];

21:dout_temp = dat_temp[42:10];

22:dout_temp = dat_temp[41:9];

23:dout_temp = dat_temp[40:8];

24:dout_temp = dat_temp[39:7];

25:dout_temp = dat_temp[38:6];

26:dout_temp = dat_temp[37:5];

27:dout_temp = dat_temp[36:4];

28:dout_temp = dat_temp[35:3];

29:dout_temp = dat_temp[34:2];

30:dout_temp = dat_temp[33:1];

31:dout_temp = dat_temp[32:0];

default:

dout_temp = 33'd0;

endcase

end

00_018m4.完整算法代码文件

V文章来源地址https://www.toymoban.com/news/detail-764988.html

到了这里,关于m基于FPGA的桶形移位寄存器verilog实现,包含testbench的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!