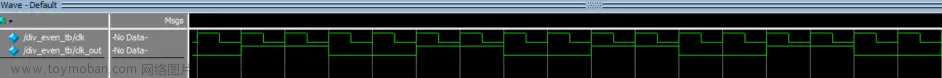

//设计分频器 将50MHZ信号分频产生1HZ的秒脉冲,输出信号占空比为50%。

//设计思路:用计数器设计,N分频:当计数到(N/2)-1个数时,输出时钟翻转一次

//50*10^6次分频:计数到24 999 999(需要25bit)时,输出信号翻转。

//无法用vmf仿真,因为endtime最大为10us,实际最少需要1000000us文章来源:https://www.toymoban.com/news/detail-766927.html

module Divider50Mhz#(

parameter clk_freq=50000000,

parameter out_freq=1)

(

input cr,clk_50M,

output reg clk_1

);

reg[24:0]count_div;

always@(posedge clk_50M or negedge cr)

begin

if(!cr)

begin

clk_1<=0; //输出被清0

count_div<=0;//计数被清0

end

else

begin

if (count_div<(clk_freq/(2*out_freq)-1))//没计够数时,保持+1

count_div<=count_div+1'b1;

else

begin

clk_1<=~clk_1;//计够数时,输出信号翻转,计数器清零

count_div<=0;

end

end

end

endmodule文章来源地址https://www.toymoban.com/news/detail-766927.html

到了这里,关于verilog---分频器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!