Xilinx 的vivado后仿或者综合后功能仿真支持各种主流仿真器包括vcs,ies(ncverilog),modelsim等。本文描述的是基于Xilinx FPGA的综合库进行网表的功能仿真或者后仿真的总结。重点是如何提取FPGA的std cell仿真模型和SDF,以及如何利用主流仿真器进行后仿。

一、采用第三方仿真器通常需要以下几个步骤:

1、 compile生成对应仿真器的仿真库(以ncverilog功能仿真为例)

打开tcl console,tcl command如下:

compile_simlib –simulator ies –directory ./ies_lib –library unisim

2、 生成仿真脚本

生成的主脚本如下:

通过稍加修改之后就可以运行。

3、 生成综合或者PR网表

该步骤是跑完综合之后,点击open synthesized design,在tcl console输入:

Write_verilog -mode funcsim <NL_name>.v -force

注意,该步骤生成的网表只能用于网表的功能仿真,不能用于带sdf的时序仿真。

二、后仿、时序仿真还需要生成sdf和PR之后的网表,步骤如下:

1、 生成带时序的仿真库:simprim

compile_simlib –simulator ies –directory ./ies_lib –library simprim –library unisim

2、 生成脚本(方法同功能仿真)

4、 生成网表和sdf

该步骤是跑完PR之后,点击open implement design,在tcl console输入:

Write_verilog -mode timesim -sdf_anno 1 -sdf_file <sdf_file_name>.sdf <NL_name>.v -force

注意,-sdf_anno一定设成1,否则时序不会反标到网表上。

Write_sdf <sdf_file_name>.sdf

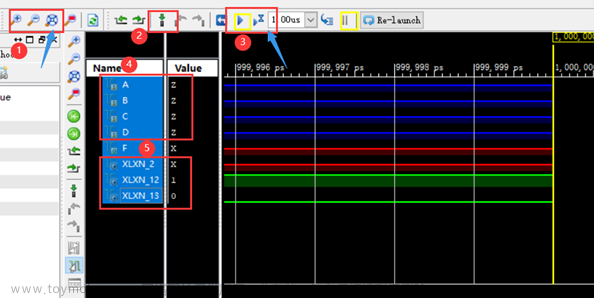

5、 脚本(uvm VIP平台下)

需要注意的是,时序仿真的库必须用simprim_ver(图中红色标记部分) 。同时,网表必须是timesim模式产生。

二 、ISE

同样使用第三方仿真工具nc-verilog进行后仿,步骤如下:

以下步骤须在工程综合和PR完之后进行。

0、 网表及sdf生成

网表和sdf放在工程的./netgen/par中。

1、 往ISE中添加第三方仿真工具

- 打开ise,Edit—>Preference->Integrated tool

2)选择编译库对应的仿真器

2、 编译仿真库 文章来源:https://www.toymoban.com/news/detail-768529.html

文章来源:https://www.toymoban.com/news/detail-768529.html

直接run,可直接生成。

3、 脚本设置 文章来源地址https://www.toymoban.com/news/detail-768529.html

文章来源地址https://www.toymoban.com/news/detail-768529.html

到了这里,关于FPGA 后仿(基于VIVADO和ISE编译库)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!