一.认识全加器

1.半加器

1.半加器的定义

半加器是能够对两个一位的二进制数进行相加得到半加和以及半加进位的组合电路。

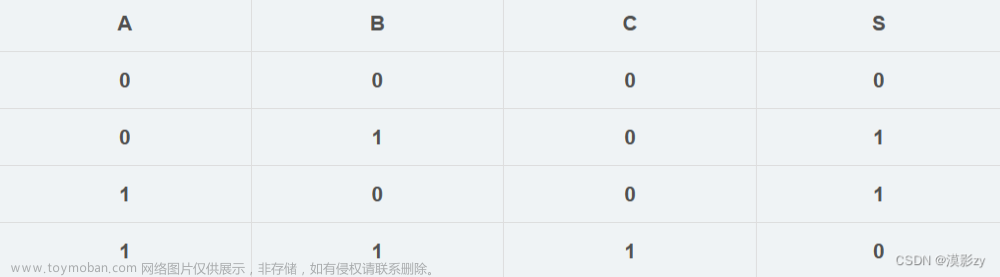

2.半加器的真值表

A,B表示二进制数,C表示半加进位,S表示半加和

| A | B | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

3.输出表达式

S = A ˉ B + A B ˉ = A ⊕ B

C = A B

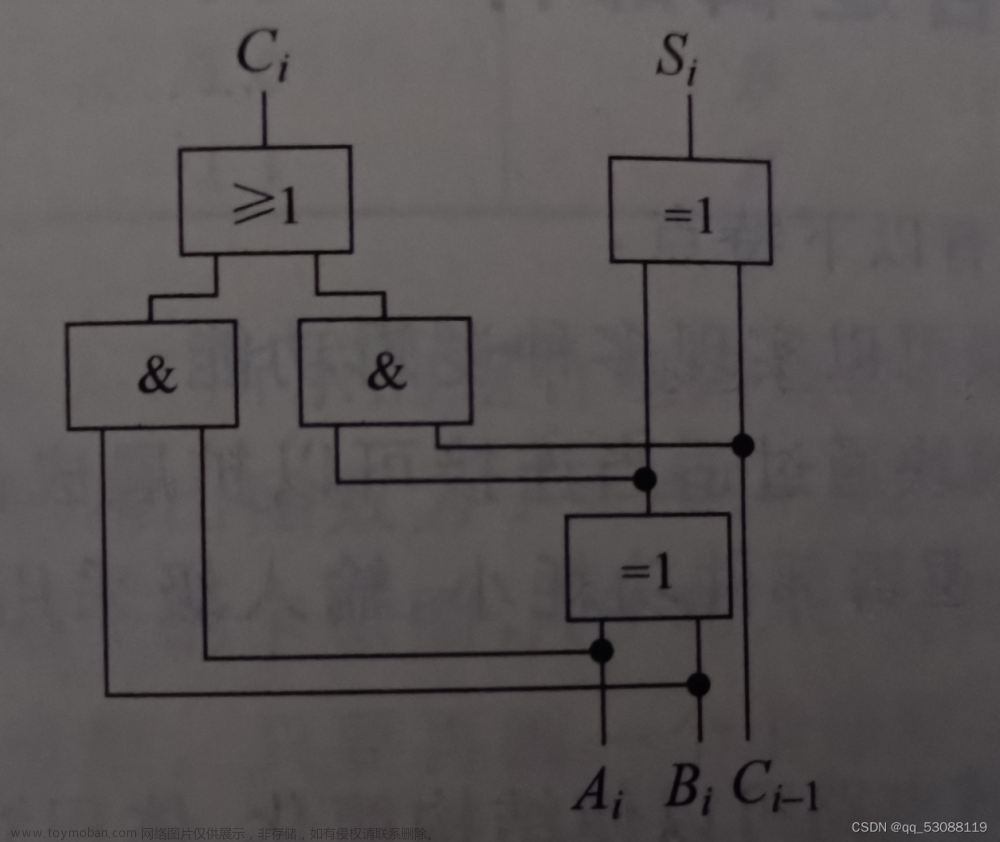

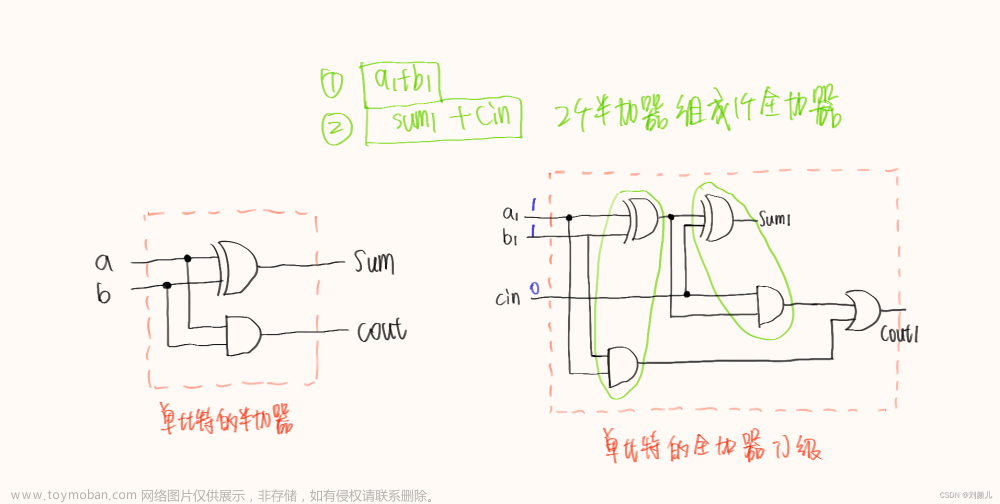

2.一位全加器

1.1位全加器的真值表

Ain表示被加数,Bin表示加数,Cin表示低位进位,Cout表示高位进位,Sum表示本位和

| Ain | Bin | Cin | Cout | Sum |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

2.输出表达式

S u m = A i n ⊕ B i n ⊕ C i n

C o u t = ( A i n ⊕ B i n ) ⋅ C i n + A i n B i n = ( A i n & B i n ) ∣ ( B i n & C i n ) ∣ ( A i n & C i n )

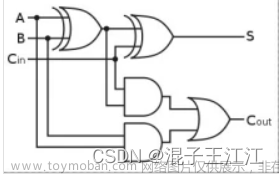

3.逻辑图

二.输入原理图实现1位加法器

创建工程过程

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

1位全加器原理图输入

绘制过程实现

首先选择File->New,进入后选择Block Diagram/Schematic File

选择元件

保存文件,并编译

通过tool->Netlist Viewers->RTL Viewer,查看电路图

三.Verilog实现1位加法器

1.创建Verilog文件

2.代码实现

module one(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

保存并编译文件

通过tool->Netlist Viewers->RTL Viewer,查看电路图’

3.仿真实现 文章来源:https://www.toymoban.com/news/detail-768677.html

文章来源:https://www.toymoban.com/news/detail-768677.html

四.测试

芯片引脚配置表

配置引脚

使用3个SW作为输入信号,2个LED作为输出信号

结果效果

通过拨动SW,观察LED的亮灭的效果,发现SW开表示1,关表示0,LED亮表示1,灭表示0。最终,验证的结果为跟其真值表相吻合。

参考文章来源地址https://www.toymoban.com/news/detail-768677.html

到了这里,关于FPGA-1位全加器的实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!