RIP计时器(以下均以华为ensp中信息为参考)

希望有需要的小伙伴可以参考参考,如有误解、请指正!

一、实验原理

1.更新计时器(Update Timer)

Update time(更新时间):指运行RIP协议的路由器向其连接口广播自己的路由信息的时间间隔(用于更新RIP路由表信息),控制RIP路由器发送更新消息的时间间隔,缺省时间为30秒,(实际上为25.5-30S间的随机数时间,这样是为了错峰发送更新,以防止所有路由器同时发送路由更新造成流量阻塞),启用了RIP的接口会发送自己的除了被水平分割抑制的路由选择表的完整副本给所有相邻的路由器。

2.无效计时器(Invalid timer)

Age time(老化时间):指路由表中每条路由信息的存活时间,如果未在指定的时间内收到此路由条目的更新信息,那此路由条目就被判定为无效路由(路由不可达),缺省时间为180S。

3.刷新计时器(Flush timer)

Garbage-collect time(垃圾收集时间):指示RIP路由器在路由信息失效后彻底清除(删除)该路由信息之前的等待时间间隔,默认为120秒。

注:刷新计时器比无效计时器时间短,这样配置的目的是为了更快地检测并刷新失效路由,以便及时更新路由表的路由信息,相当于直接跳过无效计时器,更快地更新路由表。

4.抑制计时器(Holddown Timer)——思科私有

路由器若在同一个接口上收到某条路由条目的度量值(跳数)比原来收到的度量值大,那么将启动一个抑制计时器,在抑制计时器的时间内该目的标记为不可达,直到计时器超时,路由器才可以接收有关此路由的更新信息。抑制计时器主要在RIP协议中用来防止路由环路,该计时器的原理是引用一个怀疑量,不管是真的还是假的路由消息,路由器先认为是假消息来避免路由环路。如果在抑制计时器超时后还接受该路由信息,那么这时路由器认为该消息是真的。

二、实验拓扑

三、实验详解

1.基础配置:

R1:

R2:

2.验证配置:

PS:由于此拓扑图两路由器为直连状态(priority = 0),RIP(priority = 100),R2学习到R1的路由信息是通过直连链路学习到的,所以此时查看RIP路由表是没有任何信息的。

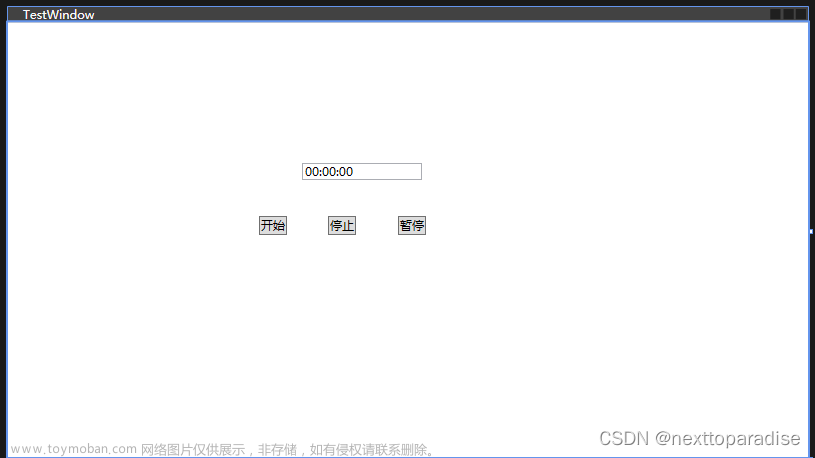

3.查看RIP计时器信息:

4.修改计时器时间:

5.查看验证:

文章来源:https://www.toymoban.com/news/detail-768793.html

文章来源:https://www.toymoban.com/news/detail-768793.html

此时可以看到三个计时器已成功修改完毕,三克油!文章来源地址https://www.toymoban.com/news/detail-768793.html

到了这里,关于RIP四大计时器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!