一、Visio图示

图1 寄存器输入输出引脚

图2 输入为高电平-例1

同步复位和异步复位都存在于时序逻辑中,与组合逻辑相比对毛刺有屏蔽作用。

图3 组合逻辑和时序逻辑的区别

当复位为高电平时,组合逻辑的结果是其输入,时序逻辑的输出需参考上升沿,此时红色虚线处的key_in为高电平,故时序逻辑的输出仍为高电平,这就解释了为什么时序逻辑与组合逻辑相比对毛刺有屏蔽作用。

图4 时序逻辑延迟一个周期

图5 输入为高低电平交错-例2

二、代码

1. rtl代码

代码如下(示例):

module flip_flop

(

input wire sys_clk,//时钟信号频率50MHz

input wire sys_rst_n,

input wire key_in,

output reg led_out

);

/* //同步复位

always@(posedge sys_clk)

if(sys_rst_n==1'b0)//复位信号低电平有效

led_out<=1'b0;//输出0

else//复位信号高电平无效

led_out<=key_in;//输入赋值给输出 */

//异步复位

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)//复位信号低有效

led_out<=1'b0;//输出0

else//复位信号无效

led_out<=key_in;//输入赋值给输出

endmodule

同步复位:当时钟为上升沿时,如果复位信号是0,则低电平有效,此时输出为0;当复位信号是1,则高电平无效,此时输出与输入一致。

异步复位:当时钟为上升沿或复位为下降沿时,如果复位信号是0,此时输出为0;当复位信号是1时,此时输出与输入一致。

2.RTL Viewer

图6 同步复位RTL Viewer图示

图7 异步复位RTL Viewer图示

3.测试文件

代码如下(示例):

`timescale 1ns/1ns

module tb_flip_flop();

reg sys_clk;

reg sys_rst_n;

reg key_in;

wire led_out;

initial

begin

sys_clk=1'b1;

sys_rst_n<=1'b0;

key_in<=1'b0;//高低都行,这里是低

#20//延迟20个时间单位,即20ns

sys_rst_n<=1'b1;//复位信号低电平有效,先拉低,复位完成后再拉高,系统才能正常工作

#210//在下降沿进行复位

sys_rst_n<=1'b0;

#40

sys_rst_n<=1'b1;//观察同步复位和异步复位的区别

end

always #10 sys_clk=~sys_clk;//每隔10ns反转一次,即一个时钟周期20ns,为50MHz

always #20 key_in<={$random}%2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:key_in=%b,led_out=%b",$time,key_in,led_out);

end

flip_flop flip_flop_inst

(

.sys_clk (sys_clk),

.sys_rst_n(sys_rst_n),

.key_in (key_in),

.led_out (led_out)

);

endmodule

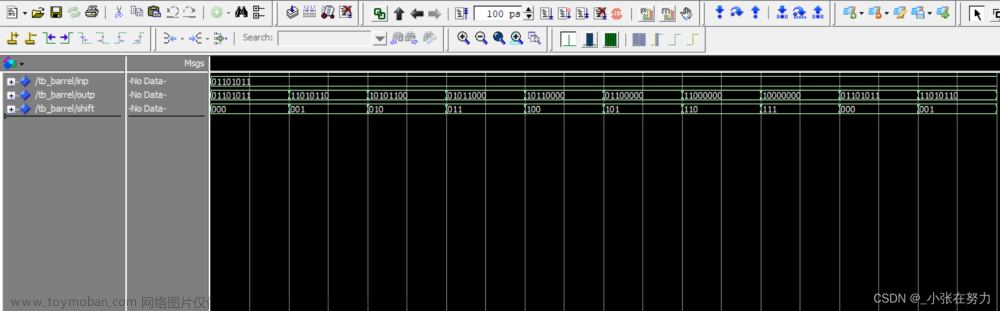

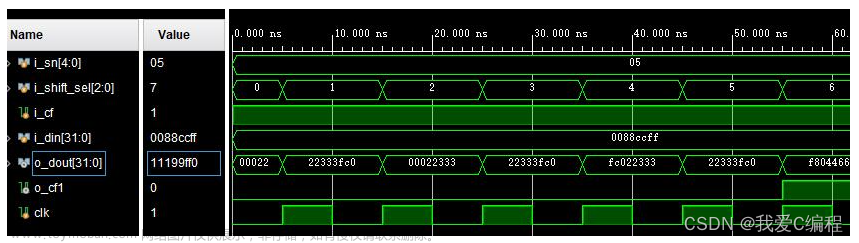

三、仿真结果

根据上面的代码仿真出的结果比较全局,没有图5所示复位全是高电平,此时将测试文件中的key_in不设置取余,而设置为1’b1,即高电平即可。

图8 同步复位仿真结果

分析参考线,即229.95ns到270ns的情况:

同步复位:左侧参考线处复位信号为0,但此时时钟是下降沿,所以输出延迟到时钟在下一个上升沿时为0;右侧参考线处复位信号为1,此时时钟是下降沿,故输出延迟到下一个上升沿才与输入一致。

图9 异步复位仿真结果文章来源:https://www.toymoban.com/news/detail-768942.html

异步复位:左侧参考线处复位信号为0,此时时钟是下降沿,但复位是下降沿,故输出立刻变为0;右侧参考线处复位信号为1,时钟是下降沿,复位信号是上升沿,故故输出延迟到下一个上升沿才与输入一致。文章来源地址https://www.toymoban.com/news/detail-768942.html

到了这里,关于Quartus实现寄存器:同步复位+异步复位的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!