1、实验目的

掌握同步四位二进制计数器 74LS161 的工作原理和设计方法

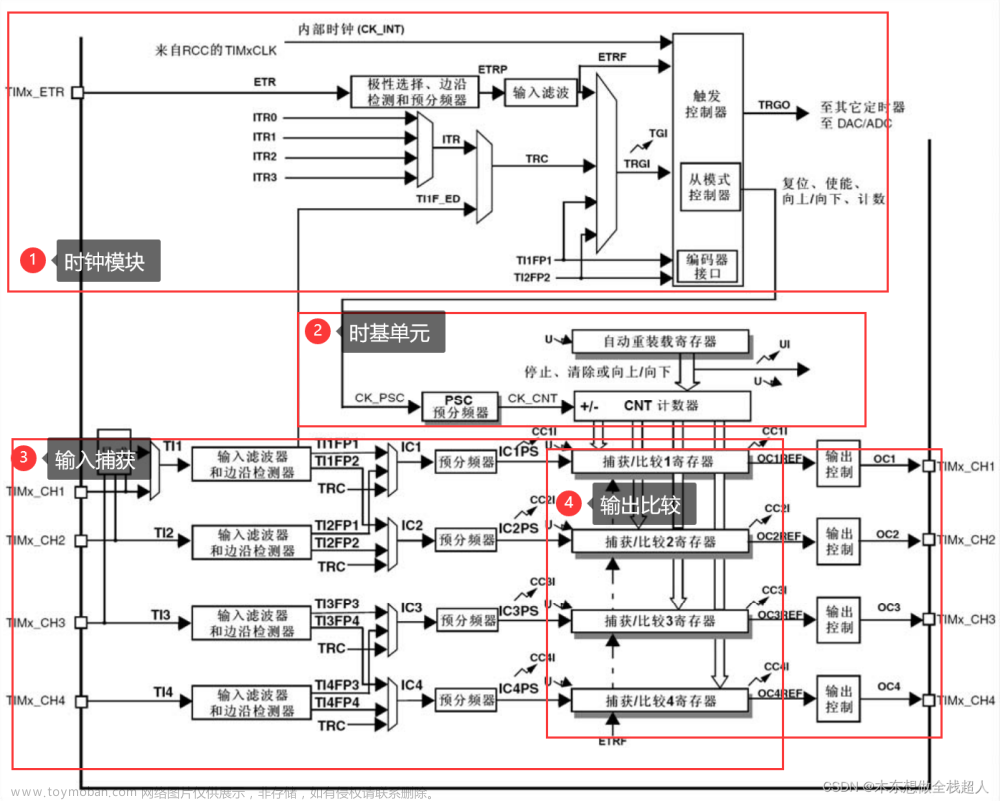

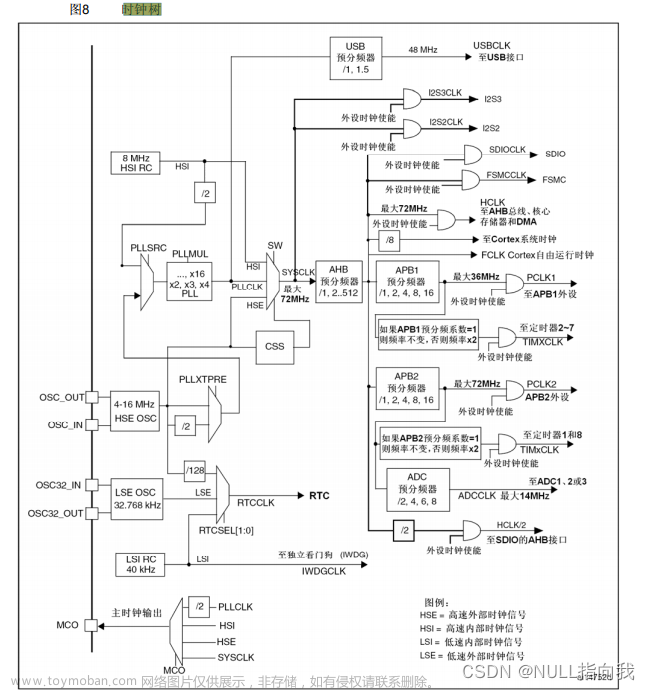

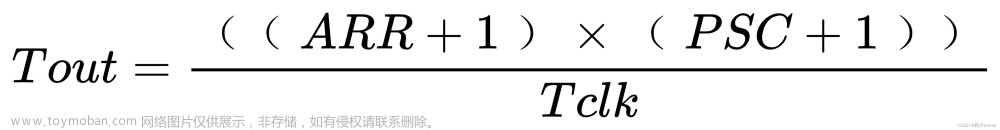

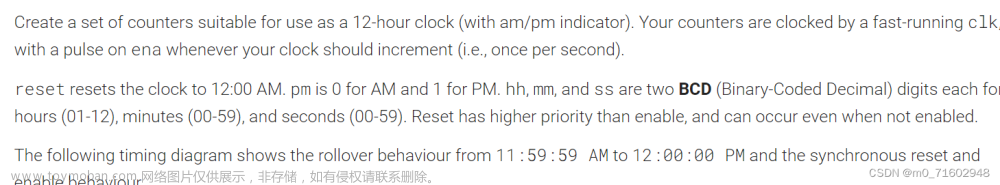

掌握时钟/定时器的工作原理与设计方法

2、实验内容

任务 1:采用行为描述设计同步四位二进制计数器 74LS161

任务 2:基于 74LS161 设计时钟应用

3、实验过程

任务 1:采用行为描述设计同步四位二进制计数器 74LS161

1.创建工程并创建 Verilog 文件

建立 HDL 类型的工程 My74LS161,创建 Verilog 文件 My74LS161, 输入 Verilog 代码

2.原理图仿真

建立基准测试波形文件My74LS161_sim.tbw,输入仿真激励信号, 在 Process 窗口中选择 Simulate Behavioral Model,可以得到仿真 波形图:

任务 2:基于 74LS161 设计时钟应用

1.创建工程并创建 Verilog 文件

建立 HDL 类型的工程 MyClock,创建 Verilog 文件 clk18,实现 128 个 clk 周期驱动秒计数,输入 Verilog 代码

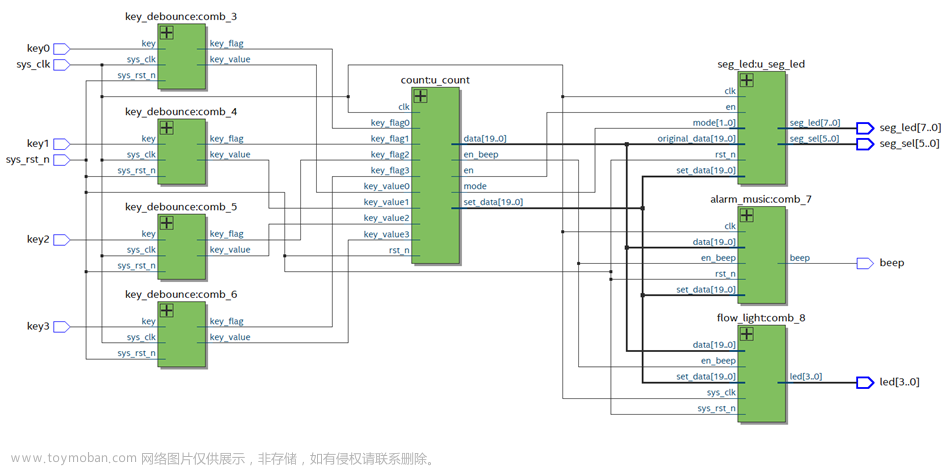

将实验 13 中的 MyMC14495、SEG65b、SLReg64b、SLReg16b、SLReg8b、 Load_Gen、SR_Latch、AND16 等文件复制到该工程目录下

创建 Verilog 文件 top,输入 Verilog 代码

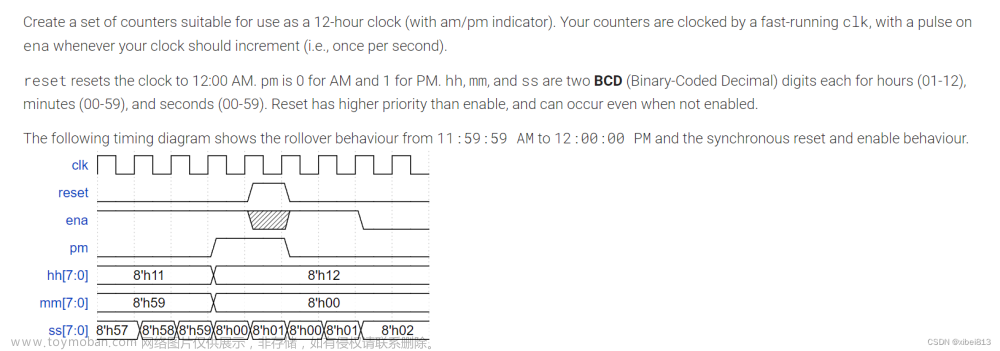

2.原理图仿真

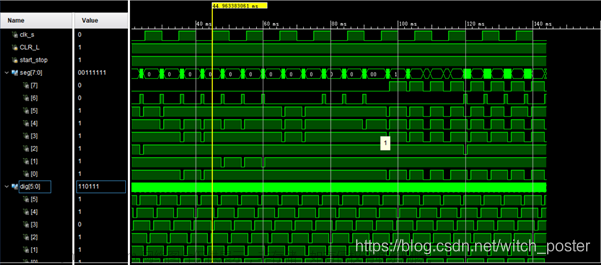

建立基准测试波形文件 clk18_sim.tbw,输入仿真激励信号,在 Process 窗口中选择 Simulate Behavioral Model,可以得到仿真波 形图:

建立基准测试波形文件 top_sim.tbw,输入仿真激励信号,在 Process 窗口中选择 Simulate Behavioral Model,可以得到仿真波 形图:

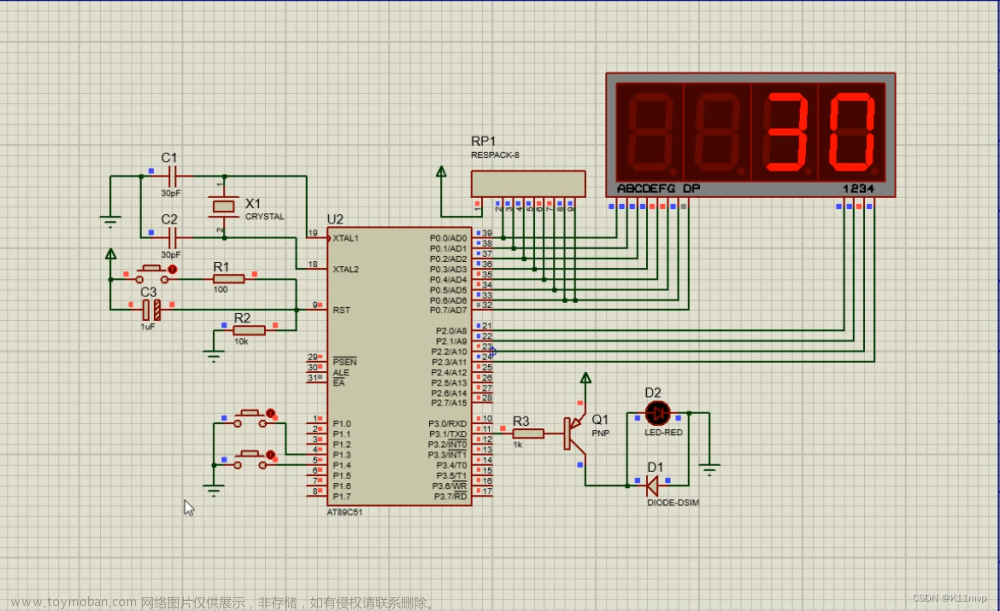

4、实验结果

实验13没能写出来,我很难受,所以这次奋发图强,肝了好几天终于肝出来了

不过我也不大想详细说明了,真的是要了老命

当时这里写的时候才发现,实验13那个有几个接口没有写

不过还好是仿真实验,我们也不用上板,就这样吧,我的这个就按照那个同学13的思路接着写了不过还是相当要命的,因为我一开始写13的时候是想用CreateNumber的,但是后来发现他这个更简单,就用了这个,不过这里缺点就体现出来了,当时生成时间、时间进位的时候写得都快吐了

对了,顺带一提,AND2,OR2这种verilog表示门的写法期末考了,还是要会的,也多亏了那个同学,期末还是写出来了,不然真的想不到会考这种东西

那么这就文章来源:https://www.toymoban.com/news/detail-769925.html

完结撒花

希望我的专栏也能给你在zd好一点的课程体验文章来源地址https://www.toymoban.com/news/detail-769925.html

到了这里,关于14、计时器、定时器设计与应用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!