目录

一、HDMI介绍

二、显示原理

2.1 DVI介绍

2.2 TMDS连接

2.2.1 TMDS编码算法

2.2.2 DVI编码

2.2.2 HDMI编码

2.3 HDMI引脚定义

三、逻辑原理图

3.1 系统框图

3.2 top原理图

3.3 核心HDMI_CTRL控制模块

3.3.1 编码功能模块

3.3.2 par_to_ser功能模块

3.3.3 顶层控制代码

四、总结

一、HDMI介绍

HDMI(High-Definition Multimedia Interface)是一种高清晰度多媒体接口,用于在各种电子设备之间传输高质量的音频和视频信号。HDMI接口常用于连接电视、显示器、投影仪、音频设备、电脑等各种消费电子设备。

HDMI接口的主要优点是可以提供高质量的数字音频和视频传输,支持高清晰度的影像输出。它可以传输全高清(1080p)甚至4K超高清分辨率的视频,以及有损和无损的多声道音频。

HDMI接口还具有多种功能和特性,例如支持3D影像传输、支持高动态范围(HDR)显示、支持音频回传(Audio Return Channel,ARC)等。它还可以传输网络数据和控制信号,以便按需连接互联网和进行设备之间的互动。

HDMI接口采用小型、方便连接的接头,相较于传统的模拟接口(如VGA、AV接口等),具有更高的传输质量和更简单的连接方式。通过使用HDMI线缆,用户可以方便地将各种电子设备连接在一起,享受高质量的音视频体验。

需要注意的是,HDMI接口有几个不同的版本(如HDMI 1.4、HDMI 2.0、HDMI 2.1等),每个版本支持不同的特性和功能。因此,在选择HDMI接口时,需要根据设备的需求和兼容性来选择适当的版本。

二、显示原理

值得注意的是HDMI是向下兼容DVI的,因此下面我们来简单的介绍一下DVI。

2.1 DVI介绍

DVI(Digital Visual Interface)是一种数字化视频接口,用于在电子设备之间传输数字视频信号。DVI接口最初是为了替代模拟接口(如VGA)而设计的,以提供更好的图像质量和更高的分辨率支持。

DVI接口支持多种视频信号格式,包括单链接(Single Link)和双链接(Dual Link)。单链接DVI可以传输较低的分辨率(如1920x1200),而双链接DVI可以支持更高的分辨率(如2560x1600)。双链接DVI还可以提供更高的带宽,支持更高的刷新率和更丰富的颜色深度。

DVI接口还可以通过适配器或转换器与其他类型的视频接口兼容,如HDMI、VGA和DisplayPort。这意味着您可以使用适当的适配器来连接DVI设备与其他类型的显示设备。

与HDMI接口相比,DVI接口没有传输音频信号的能力。因此,在连接DVI设备时,您可能需要另外使用音频线缆来传输音频信号。

总的来说,DVI接口是一种常见的数字视频接口,可用于连接计算机显示器、显卡、投影仪等设备。它提供了较高的图像质量和分辨率支持,是一个可靠且广泛使用的接口标准。然而,由于它不支持音频传输并且逐渐被HDMI和DisplayPort等接口所替代,因此在选择设备时需要考虑其兼容性和功能需求。

2.2 TMDS连接

TMDS(Transition Minimized Differential Signaling)是一种用于传输数字信号的技术,常用于接口标准如DVI和HDMI中。

TMDS连接通过使用差分信号传输来减少信号干扰和损失。它使用一对相互翻转的信号线(正负两条)传输数据。通过将数据分成多个位(bit)并使用时钟信号进行同步,TMDS可以高效地传输大量的数字数据。

在TMDS连接中,发送方将数字信号转换为差分信号,即将每个位的高低电平分别对应为正负两个电平。接收方通过比较两个差分信号的电平差异来恢复原始的数字信号。这种差分传输方式能够减少电磁干扰和传输距离上的信号损失,从而提供更可靠的数据传输。

TMDS连接常用于视频接口标准,如DVI和HDMI。在DVI接口中,TMDS连接用于传输图像数据。在HDMI接口中,TMDS连接不仅可以传输视频数据,还可以传输音频和其他控制信号。

总的来说,TMDS连接是一种通过差分信号传输数字数据的技术。它在数字接口标准中起到了重要的作用,提供了可靠和高质量的数据传输。

其中包括T.M.D.S.transmitter编码过程,具体TMDS编码算法如下:

2.2.1 TMDS编码算法

TMDS编码算法主要是将8bit的数据扩展为10bit的数据,以方便进行解码。

TMDS编码算法在官网也有提供,地址为:amd - Sign In

2.2.2 DVI编码

在传软视频图像的过程中,数据通道上传输的是编码后电有效像素字符。

而在每一帧图像的行与行之间,以及视频中不同帧之间的时间间隔(消隐期)内,数据通道上传输的则是控制字符。

每个通道上有两位控制信号的输入接口,共对应四种不同的控制字符。

这些控制字符提供了视频的行同步(HZYNC)以及帧同步(VSYNC)信息,在蓝色通道传输。

2.2.2 HDMI编码

HDMI传输的消隐期除了控制字符之外,还可以用于传输音频或者其他附加数据,比如字幕信息等。

4-bit音频和附加数据将通过TERC4编码机制转换成10-bit TERC4字符,然后在绿色和红色通道上传输。

这里为了简单流程,因此采用DVI编码与TMDS编码算法。

2.3 HDMI引脚定义

三、逻辑原理图

3.1 系统框图

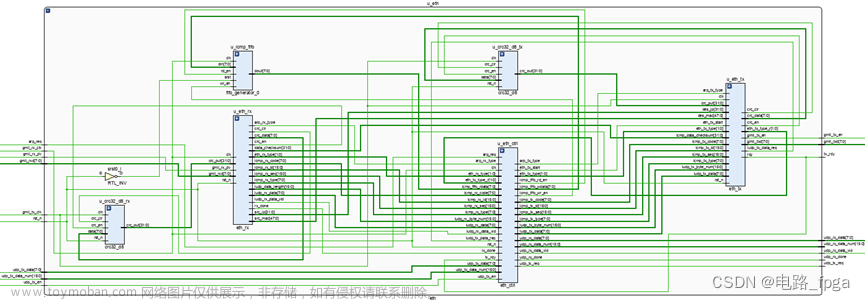

3.2 top原理图

3.3 核心HDMI_CTRL控制模块

3.3.1 编码功能模块

其中encode采用官方提供的代码。

3.3.2 par_to_ser功能模块

其中主要包括并转串、单脉冲信号转换为差分信号。

1、并转串模块

注:主要使用OSERDESE2原语,具体参考手册。

`timescale 1ns / 1ps

module par_to_ser(

input [9:0] paralell_data,

input clk_5x,

input reset,

input paralell_clk,

output serial_data_out

);

wire cascade1;

wire cascade2;

//例化OSERDESE2原语,实现并串转换,Master模式

OSERDESE2 #(

.DATA_RATE_OQ ("DDR"), // 设置双倍数据速率

.DATA_RATE_TQ ("SDR"), // DDR, BUF, SDR

.DATA_WIDTH (10), // 输入的并行数据宽度为10bit

.SERDES_MODE ("MASTER"), // 设置为Master,用于10bit宽度扩展

.TBYTE_CTL ("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC ("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_Master (

.CLK (clk_5x), // 串行数据时钟,5倍时钟频率

.CLKDIV (paralell_clk), // 并行数据时钟

.RST (reset), // 1-bit input: Reset

.OCE (1'b1), // 1-bit input: Output data clock enable

.OQ (serial_data_out), // 串行输出数据

.D1 (paralell_data[0]), // D1 - D8: 并行数据输入

.D2 (paralell_data[1]),

.D3 (paralell_data[2]),

.D4 (paralell_data[3]),

.D5 (paralell_data[4]),

.D6 (paralell_data[5]),

.D7 (paralell_data[6]),

.D8 (paralell_data[7]),

.SHIFTIN1 (cascade1), // SHIFTIN1 用于位宽扩展

.SHIFTIN2 (cascade2), // SHIFTIN2

.SHIFTOUT1 (), // SHIFTOUT1: 用于位宽扩展

.SHIFTOUT2 (), // SHIFTOUT2

.OFB (), // 以下是未使用信号

.T1 (1'b0),

.T2 (1'b0),

.T3 (1'b0),

.T4 (1'b0),

.TBYTEIN (1'b0),

.TCE (1'b0),

.TBYTEOUT (),

.TFB (),

.TQ ()

);

//例化OSERDESE2原语,实现并串转换,Slave模式

OSERDESE2 #(

.DATA_RATE_OQ ("DDR"), // 设置双倍数据速率

.DATA_RATE_TQ ("SDR"), // DDR, BUF, SDR

.DATA_WIDTH (10), // 输入的并行数据宽度为10bit

.SERDES_MODE ("SLAVE"), // 设置为Slave,用于10bit宽度扩展

.TBYTE_CTL ("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC ("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH (1) // 3-state converter width (1,4)

)

OSERDESE2_Slave (

.CLK (clk_5x), // 串行数据时钟,5倍时钟频率

.CLKDIV (paralell_clk), // 并行数据时钟

.RST (reset), // 1-bit input: Reset

.OCE (1'b1), // 1-bit input: Output data clock enable

.OQ (), // 串行输出数据

.D1 (1'b0), // D1 - D8: 并行数据输入

.D2 (1'b0),

.D3 (paralell_data[8]),

.D4 (paralell_data[9]),

.D5 (1'b0),

.D6 (1'b0),

.D7 (1'b0),

.D8 (1'b0),

.SHIFTIN1 (), // SHIFTIN1 用于位宽扩展

.SHIFTIN2 (), // SHIFTIN2

.SHIFTOUT1 (cascade1), // SHIFTOUT1: 用于位宽扩展

.SHIFTOUT2 (cascade2), // SHIFTOUT2

.OFB (), // 以下是未使用信号

.T1 (1'b0),

.T2 (1'b0),

.T3 (1'b0),

.T4 (1'b0),

.TBYTEIN (1'b0),

.TCE (1'b0),

.TBYTEOUT (),

.TFB (),

.TQ ()

);

endmodule

3.3.3 顶层控制代码

里面例化编码模块、并转串、以及OBUFDS原语(单脉冲信号转换为差分信号)。还要一个复位信号的转化。文章来源:https://www.toymoban.com/news/detail-770022.html

注:转换复位信号

module asyn_rst_syn(

input clk, //目的时钟域

input reset_n, //异步复位,低有效

output syn_reset //高有效

);

//reg define

reg reset_1;

reg reset_2;

assign syn_reset = reset_2;

//对异步复位信号进行同步释放,并转换成高有效

always @ (posedge clk or negedge reset_n) begin

if(!reset_n) begin

reset_1 <= 1'b1;

reset_2 <= 1'b1;

end

else begin

reset_1 <= 1'b0;

reset_2 <= reset_1;

end

end

endmodulemodule dvi_transmitter_top(

input pclk, // pixel clock

input pclk_x5, // pixel clock x5

input reset_n, // reset

input [23:0] video_din, // RGB888 video in

input video_hsync, // hsync data

input video_vsync, // vsync data

input video_de, // data enable

output tmds_clk_p, // TMDS 时钟通道

output tmds_clk_n,

output [2:0] tmds_data_p, // TMDS 数据通道

output [2:0] tmds_data_n,

output tmds_oen // TMDS 输出使能

);

//wire define

wire reset;

//并行数据

wire [9:0] red_10bit;

wire [9:0] green_10bit;

wire [9:0] blue_10bit;

wire [9:0] clk_10bit;

//串行数据

wire [2:0] tmds_data_serial;

wire tmds_clk_serial;

//*****************************************************

//** main code

//*****************************************************

assign tmds_oen = 1'b1;

assign clk_10bit = 10'b1111100000;

//异步复位,同步释放

asyn_rst_syn reset_syn(

.reset_n (reset_n),

.clk (pclk),

.syn_reset (reset) //高有效

);

//对三个颜色通道进行编码

dvi_encoder encoder_b (

.clkin (pclk),

.rstin (reset),

.din (video_din[7:0]),

.c0 (video_hsync),

.c1 (video_vsync),

.de (video_de),

.dout (blue_10bit)

) ;

dvi_encoder encoder_g (

.clkin (pclk),

.rstin (reset),

.din (video_din[15:8]),

.c0 (1'b0),

.c1 (1'b0),

.de (video_de),

.dout (green_10bit)

) ;

dvi_encoder encoder_r (

.clkin (pclk),

.rstin (reset),

.din (video_din[23:16]),

.c0 (1'b0),

.c1 (1'b0),

.de (video_de),

.dout (red_10bit)

) ;

//对编码后的数据进行并串转换

serializer_10_to_1 serializer_b(

.reset (reset), // 复位,高有效

.paralell_clk (pclk), // 输入并行数据时钟

.serial_clk_5x (pclk_x5), // 输入串行数据时钟

.paralell_data (blue_10bit), // 输入并行数据

.serial_data_out (tmds_data_serial[0]) // 输出串行数据

);

serializer_10_to_1 serializer_g(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (green_10bit),

.serial_data_out (tmds_data_serial[1])

);

serializer_10_to_1 serializer_r(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (red_10bit),

.serial_data_out (tmds_data_serial[2])

);

serializer_10_to_1 serializer_clk(

.reset (reset),

.paralell_clk (pclk),

.serial_clk_5x (pclk_x5),

.paralell_data (clk_10bit),

.serial_data_out (tmds_clk_serial)

);

//转换差分信号

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS0 (

.I (tmds_data_serial[0]),

.O (tmds_data_p[0]),

.OB (tmds_data_n[0])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS1 (

.I (tmds_data_serial[1]),

.O (tmds_data_p[1]),

.OB (tmds_data_n[1])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS2 (

.I (tmds_data_serial[2]),

.O (tmds_data_p[2]),

.OB (tmds_data_n[2])

);

OBUFDS #(

.IOSTANDARD ("TMDS_33") // I/O电平标准为TMDS

) TMDS3 (

.I (tmds_clk_serial),

.O (tmds_clk_p),

.OB (tmds_clk_n)

);

endmodule四、总结

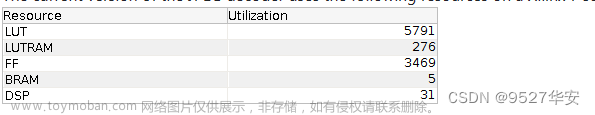

HMDI的控制模块整体代码并不复杂,但是需要整体理解逻辑思路。同时需要熟练的使用原语的使用。文章来源地址https://www.toymoban.com/news/detail-770022.html

到了这里,关于FPGA——基于verilog编写HDMI接口屏幕显示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!