目录

目录

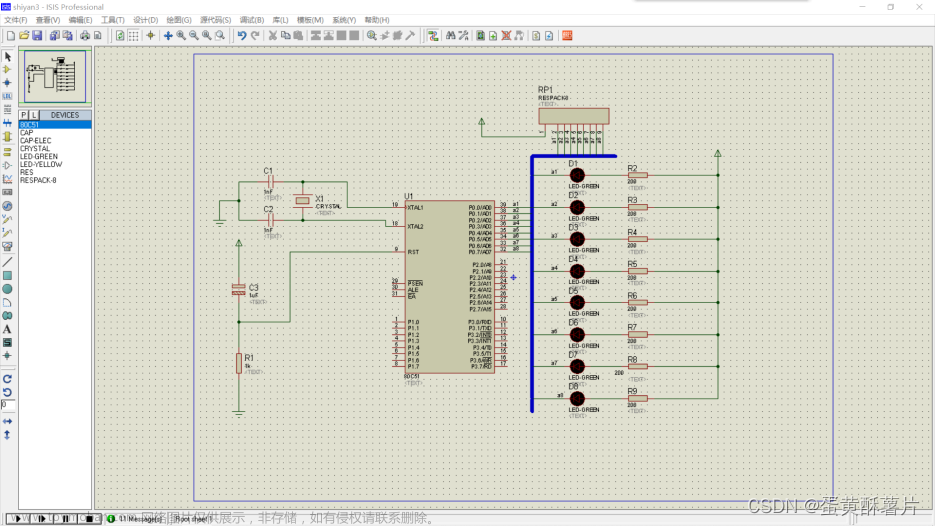

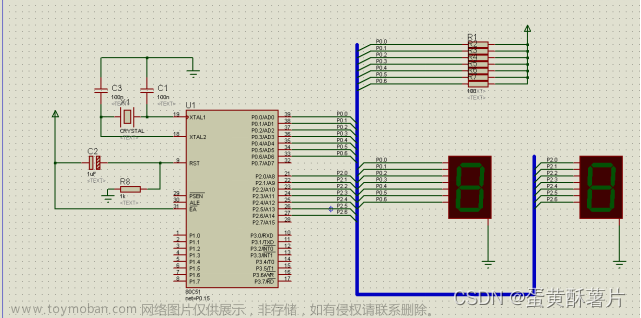

一、硬件组成

AT89S51单片机片内结构

AT89S51引脚功能

3.并行I/O口引脚

P0口

P0口:地址/数据总线

数据输出

数据输入

P0口:通用输入输出功能

P1口

P2组I/O引脚编辑

用作地址线

数据输出

数据输入,

用作通用I/O口

数据输出

数据输入(读取引脚电平状态)

P3口

第一功能(通用输入输出功能)

输出

第二功能:

输出

输入

时钟电路设计

内部时钟方式

外部时钟方式

机器周期,指令周期,与指令时序。

时钟周期

机器周期

指令周期

复位操作和复位电路(硬件复位)

看门狗:

单片机系统受到干扰可能会引起程序“跑飞”或 “死循环”,使系统失控。

使用方法:

一、硬件组成

AT89S51单片机片内结构

8位微处理器(CPU)

数据存储器(128B RAM)

程序存储器(4KB Flash ROM);

4个8位可编程并行I/O口(P0口、P1口、P2口、P3口);

1个全双工的异步串口

一个看门狗定时器

2个16位的定时器/计数器

5个系统中断源(对应五个中断向量)

特殊功能寄存器(SFR)26个

附:单片机还内含:3个程序加密锁定位;

低功耗模式有空闲模式和掉电模式,且具有掉电模式下的中断恢复模式

CPU

8位,与通用CPU基本相同,包含运算器,控制器,还有额外的区别于微机的位处理功能

数据存储器(RAM)

片内为128B(52系列为256B),片外可扩展到64KB

程序存储器(4KB Flash ROM);

片内集成4KB的Flash存储器,片外可扩展至64KB

中断系统

内含5个中断源 具备两级中断优先权处理机制

定时器/计数器

2个十六位定时器/计数器(52系列有3个),支持四种工作模式,

串行口

一个异步的全双工的异步串行口,4种工作方式,可进行串行通信,扩展并行I/O口,还可与多个单片机构成多机通信系统。

特殊功能寄存器

26个,对片内各功能部件管理、控制和监视。是各功能件的控制寄存器和状态寄存器,映射片内RAM区80H~FFH内。

看门狗定时器

当程序执行被干扰或者陷入不应该进入的死循环,或者跑飞时,使程序可恢复正常运行

AT89S51引脚功能

AT89S51目前多采用双列直插,此外还有44引脚的PLCC和TQFP封装方式的芯片。

引脚按功能可以分为3个模块

1.时钟及电源模块(XTAL1 XTAL2 Vcc Vss)

2.控制引脚(PSEN*、ALE/PROG*、EA*/VPP、RST(RESET)

3.I/O引脚 (四组P0 P1 P2 P3 每组又有8个I/O口)

时钟及电源模块(XTAL1 XTAL2 Vcc Vss)

Vcc:+5V电源

Vss:数字地

XTAL1:片内振荡器反向放大电路和时钟发生器电路输入端,用片内振荡器时,该脚接外部石英晶体和微调电容。外接时钟源时,该脚接来自外部时钟振荡器的信号。

XTAL2:片内振荡器反相放大器的输出端。当使用片内振荡器,该脚接外部石英晶体和微调电容。当使用外部时钟源时,本脚悬空。

控制引脚:

RST(RSET):复位 要求在引脚上添加持续时间大于2个机器周期的高电平,可使单片机复位,正常工作时,该引脚电平应低于0.5V

EA*/VPP (Enable Address/Voltage Pulse of Programing):可分时复用两个功能做第一功能(/EA)时:外部程序存储区访问允许控制端,为0只允许读取片外,片内的不起作用

vpp:第二功能:(即EA=1)在PC值小于0XFFFH时候,单片机默认读取片内FLASH存储器(4KB)当pc>0XFFFH,指向片外60KB程序存储空间的程序

ALE/PROG*(Address Latch Enable/PROGramming)

ALE:CPU访问外部程序存储器或外部数据存储器提供地址锁存控制信号,将低8位地址锁存在片外的地址锁存器中(由于引脚数目过少,所以采用分时复用模式)

此外,单片机正常运行时,ALE端一直有正脉冲信号输出,此频率为fosc的1/6。该信号可作外部定时或触发信号使用。 如果不需要输出正脉冲可于AUXR辅助寄存器设置禁止,但不影响正常输出高低电平,只是禁止输出正脉冲信号

同时:每单AT89S51访问外部RAM或I/O时,会丢失一个脉冲,因此信号频率并不是准确的fosc1/6

PROG*:引脚第二功能,对片内Flash编程,加编程脉冲输入。

PSEN* (Program Strobe ENable):片外程序存储器读选通信号,低电平有效。

3.并行I/O口引脚

P0口

P0口:P0.0-P0.7,共8位。漏极开路的双向I/O口

ps:漏极开路输出无法输出高电平,只能输出低电平或者高阻状态,如果需要输出高电平,虚外接上拉电阻sh总线(输入输出"0"/"1",此时为双向),也可以作为通用I/O口(输出高低电平,此时为准双向)

P0口内部结构如上图所示:

多路开关MUX:受控制引脚控制,用于选通是作为地址/数据总线,还是通用I/O口,当控制引脚为高电平时,多路开关接受来自,地址/数据总线的电平信息,当控制信号为低电平时,多路开挂与D触发器相连接

D触发器:用于数据的缓存,当D触发器接收到来自CP端的脉冲信号,触发器就会接收来自D端输入的信号,并持续的将数据输出到Q端以及反向端/Q。

P0口:地址/数据总线

当P0口用作数据总线时(外扩外部存储器,或扩展I/O口时),常与P2口构成16位地址总线,P0口引脚作为低八位地址总线,P2口引脚作为高八位地址总线,可寻址64KB地址空间。

数据输出

P0.X作为输出时,控制信号为高电平,多路开关不与D触发器连接,当地址信号为高电平时,与门导通,T1输出高电平,T2截止,此时I/0口可测得为高电平。当地址信号为低电平时,T1截止,T2导通,此时I/O输出为低电平

数据输入

P0.X作为输入时,由于上电复位后,所有I/O口寄存器默认为0X00,故不用事先向D触发器写1,使T2截止。当作为数据输入时,控制信号为低电平(此时T1截止),多路开关MUX与D触发器相连接。T1,T2均截止,输出功能被禁止,P0.X为高阻状态,外部输入数据,由P0.X端口输入,通过下方三态缓冲器,输入到数据总线。

P0口:通用输入输出功能

此时控制信号为低电平,此时T1截止,无法输出高电平,多路开关MUX与D触发器连接

输出:

当触发器为1时,Q反端输出低电平,T1已经被截止了,此时形成漏极开路电路,T2被截止,由于单片机的输出信号能力极弱,如果需要输出高电平,需要在P0.x引脚外接上拉电阻,通常上拉电阻选择10KΩ,此时电流从上拉电阻流向负载,此电流称为拉电流,其大小由上拉电阻决定。

当触发器为1时,Q反端输出高电平,T2已经被导通了,此时P0.X引脚接地,此时电流从负载流向I/O口,此电流称为灌电流,P0.X允许的灌电流大小,最大值为12mA。

输入(读取引脚电平状态):

当P0.x作为输入时,分读取引脚电平状态和读取触发器输出状态,此处我们仅介绍读取引脚电平状态的方法,

temp = P0 //将P0组引脚状态保存至temp变量读取触发器输出状态,即读取锁存触发器Q的输出状态,当锁存触发器的触发信号为高电平时,读取触发器Q端状态

P0 = P0 << 1 //读取P0组引脚的状态逻辑左移,并再次赋值给P0运行此处代码时,CPU先从触发器读取Q端状态,然后再将其值左移后,再将运算完毕后的值赋给P0。

P1口

P1组引脚内含上拉电阻,没有多路开关,只能作为通用I/O口

操作方式原理,同P1作为通用I/O口时操作方式。

P2组I/O引脚

有两种工作方式

当P2口用作数据总线时(外扩外部存储器,或扩展I/O口时),常与P1口构成16位地址总线,P0口引脚作为低八位地址总线,P2口引脚作为高八位地址总线,可寻址64KB地址空间。

用作地址线

数据输出

控制信号为高电平,多路开关与地址线导通,当地址/数据输出为高电平时,经过非门输出为低电平,mos管截止,IO口输出高电平,反之当地址/数据输出为低电平时,经过非门输出为高电平,mos管导通,IO口接地,输出低电平

数据输入,

控制信号为低电平,多路开关与锁存触发器导通,读取数据信号时,必须先向内部总线写1,I/O口接内部上拉电阻,输出高电平,接收来自外界的低电平。

用作通用I/O口

数据输出

当触发器值为1时,Q端输出高电平,经过非门,变为低电平,MOS管截止,I/O口引脚端连接内部上拉电阻,输出高电平状态,

当触发器值为0时,Q端输出低电平,经过非门,变为高电平,MOS管导通,I/O口引脚端接地,输出低电平状态,

数据输入(读取引脚电平状态)

读取P2口引脚电平状态时,必须先向内部总线必须先向内部总线写1,I/O口接内部上拉电阻,输出高电平,接收来自外界的低电平。

P3口

由于AT89S51的引脚数目有限,因此在P3口电路中增加了引脚的第二功能

P3口的每一位都可分别定义为第二输入功能或第二输出功能。字节地址为B0H,位地址为B0H~B7H。

第一功能(通用输入输出功能)

此时第二输出功能信号保持为高电平,使与非门输出状态仅受触发器Q端的影响

输出

触发器信号为高电平时,经过与非门变为低电平,MOS管截止,I/O引脚内接上拉电阻,输出高电平。触发器信号为低电平时,经过与非门变为高平,MOS管导通,I/O引脚内接地,输出地电平。

输入(读取I/O引脚电平状态)

先向内部总线写"1",I/O口输出电平为高电平,接收来自外部的电平信号,输入的信息通过读引脚后进入内部总线,单片机上电后默认为P3寄存器的值为0xFF.第二功能:

输出

第二输出引脚为高电平,且Q端为保持在高电平,此时启用第二功能,与非门输出低电平,MOS管截止,P3引脚内接上拉电阻,输出高电平,当第二功能输出引脚为低电平时,输出低电平

输入

输入功能与第一功能方法一致

时钟电路设计

单片机严格在时钟电路信号控制下运行,失去时钟电路,单片机将无法工作。时钟频率直接影响单片机的运行速度,以及时钟电路质量也直接影响系统的稳定性。

执行指令时,CPU首先到程序存储器中取出需要执行的指令操作码,然后译码,并由时序电路产生一系列控制信号完成指令所规定的操作。

CPU发的时序信号两类,一类用对片内各个功能部件控制,用户无须了解;另一类用于对片外存储器或I/O端口的控制,这部分时序对于分析、设计硬件接口电路至关重要。

常用时钟电路方式分为内部时钟方式和外部时钟方式,AT89S51最高时钟频率为32MHz

内部时钟方式

AT89S51内部有一个用于构成振荡器的高增益反相放大器,输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体振荡器和微调电容,构成一个稳定的自激振荡器

电路中的电容 C1和 C2 的典型值通常选择为 30pF或者33pF。晶体振荡频率的范围通常是在 1.2~12MHz。AT89S51单片机常选择振荡频率6MHz或12MHz的石英晶体。

外部时钟方式

用现成的外部振荡器产生脉冲信号,常用于多片AT89S51同时工作,以便于多片AT89S51单片机之间的同步。

外部时钟源直接接到XTAL1端,XTAL2端悬空

时钟信号输出:由于单片机的驱动能力并不强,所以需要引出

机器周期,指令周期,与指令时序。

时钟周期

时钟控制信号的基本时间单位。若晶振频率为fosc,则时钟周期Tosc=1/fosc。如fosc=6MHz,Tosc=166.7ns

机器周期

CPU完成一个基本操作所需时间为机器周期。执行一条指令分为几个机器周期。每12个时钟周期为1个机器周期

指令周期

执行一条指令所需的时间。简单的单字节指令,取出指令立即执行,只需一个机器周期的时间。而有些复杂的指令,如转移、乘、除指令则需两个或多个机器周期

复位操作和复位电路(硬件复位)

为什么需要添加复位电路,当程序跑飞,或操作系统陷入死锁时,就需要复位操作,

给复位脚RST加上大于2个机器周期(即24个时钟振荡周期)的高电平就使AT89S51复位

复位后各寄存器状态

看门狗:

单片机系统受到干扰可能会引起程序“跑飞”或 “死循环”,使系统失控。

使用一个定时器不断技术监视系统的运行,当看门狗启动后,为防止看门狗不必要的溢出,需要定时喂狗,否则,将触发看门狗,引起系统复位

使用方法:

看门狗内部含一个14位的定时器和看门狗复位寄存器,开启看门狗后,定时器会自动对系统时钟12分频后的信号计数,当计数满到16384后,产生一个高电平复位信号,使单片机复位。

看门狗的启动和清0的方法是一样的,用户只要向寄存器WDTRST(地址为A6H)先写入1EH,接着写入E1H,看门狗便启动计数。为防止看门狗启动后产生不必要的溢出,在执行程序的过程中,应在16384µs内不断地复位清“0”文章来源:https://www.toymoban.com/news/detail-770384.html

在C51语言编程中,若使用看门狗功能,由于头文件reg51.h中,并没有声明WDTRST寄存器,所以必须先声明WDTRST寄存器。文章来源地址https://www.toymoban.com/news/detail-770384.html

在C51语言编程中,若使用看门狗功能,由于头文件reg51.h中,并没有声明WDTRST寄存器,

所以必须先声明WDTRST寄存器。

sfr WDTRST=0xa6

声明后可以用命令启动或复位看门狗。

WDTRST=0x1e;

WDTRST=0xe1;

#include<reg51.h>

sfr WDTRST=0xa6

main( )

{

…… ;

WDTRST=0x1e; //启动看门狗运行

WDTRST=0xe1;

while(1) //无限循环

{

WDTRST=0x1e; //清0并启动看门狗运行

WDTRST=0xe1;

……; //执行时间必须小于16384µs(系统时钟为12MHz时)

}

}到了这里,关于单片机原理与应用设计第二章(AT89S51)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!