名称:Quartus数字秒表verilog代码青创QC-FPGA开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

数字秒表设计

1、支持复位、启动、暂停

2、具有量程切换功能,可以切换显示小时、分钟或者秒、毫秒

3、数码管显示时间,精确到10毫秒

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

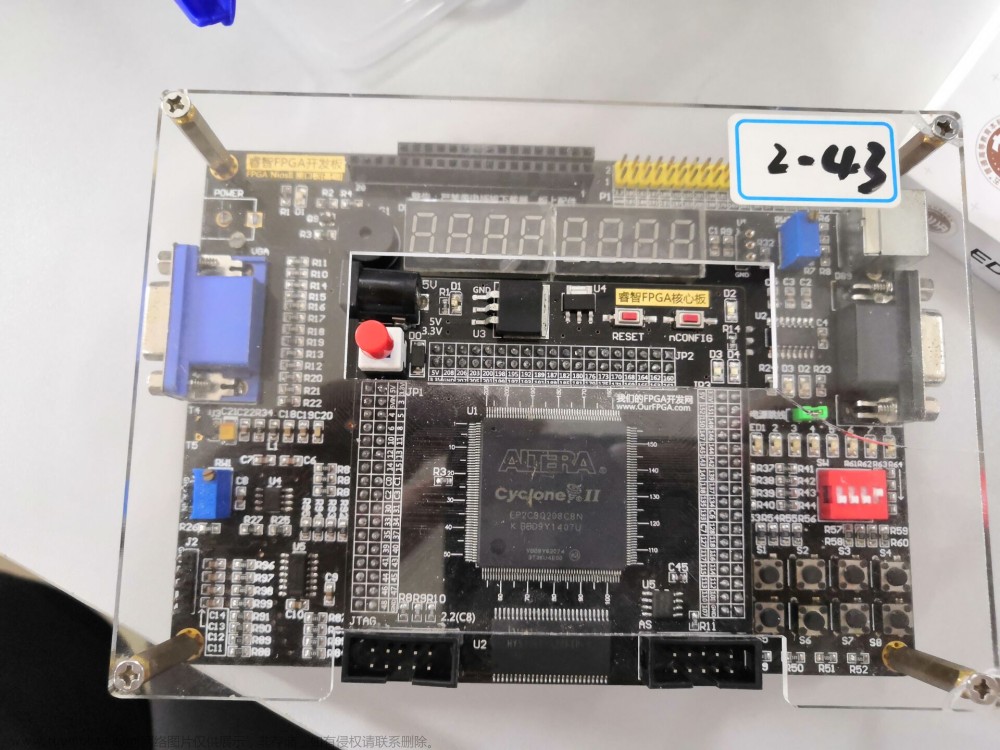

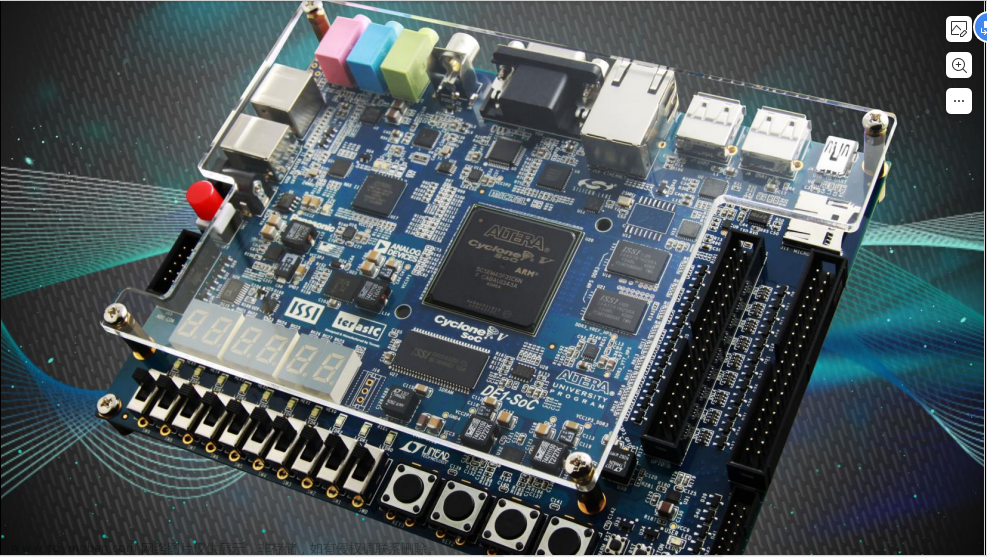

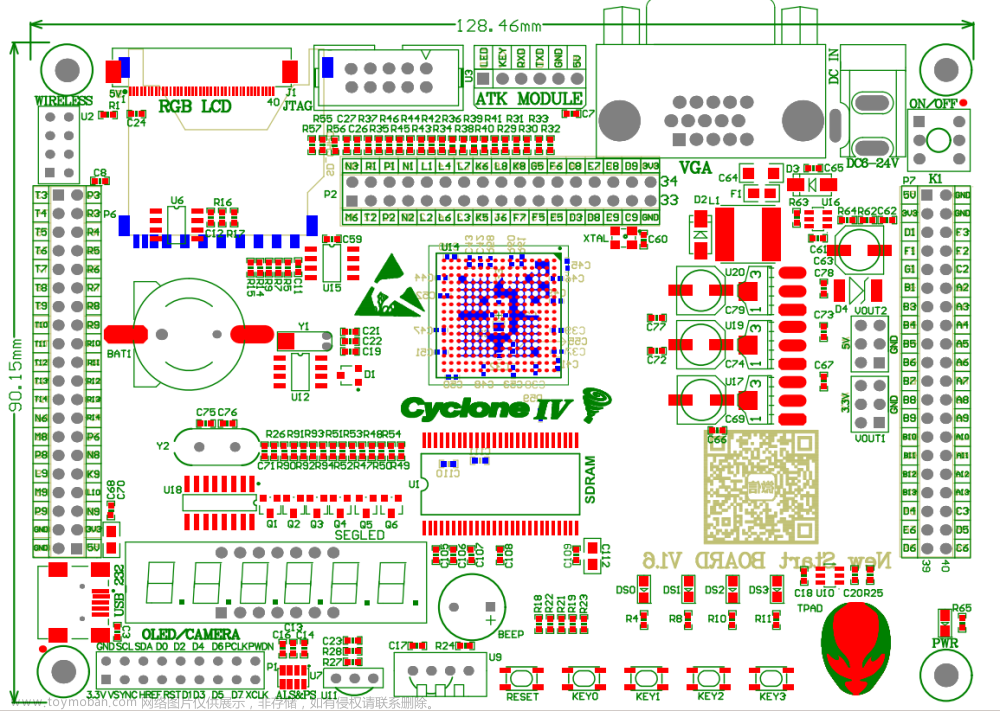

本代码已在青创QC-FPGA开发板验证,青创QC-FPGA开发板如下,其他开发板可以修改管脚适配:

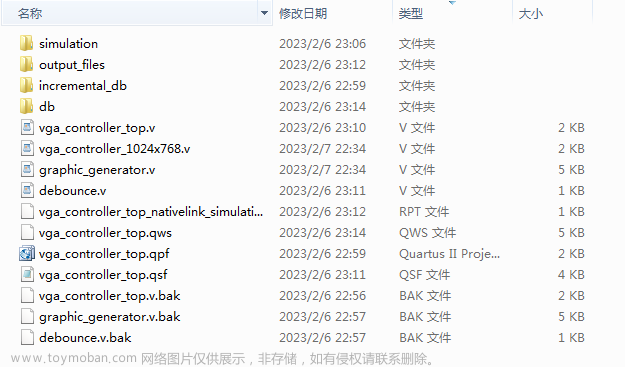

1. 工程文件

2. 程序文件

3. 程序编译

4. 管脚分配

5. RTL图

6. 仿真图

顶层整体仿真图

分频模块

控制模块

显示模块

部分代码展示:文章来源:https://www.toymoban.com/news/detail-771439.html

LIBRARY ieee; USE ieee.std_logic_1164.all; --秒表设计 ENTITY miaobiao IS PORT ( sysclk_in : IN STD_LOGIC;--48MHZ S1 : IN STD_LOGIC;--复位 S2 : IN STD_LOGIC;--启动 S3 : IN STD_LOGIC;--停止 sw_in : IN STD_LOGIC;--量程切换 LEDA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管段选 SEL : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--数码管位选 ); END miaobiao; ARCHITECTURE RTL OF miaobiao IS --参数化的分频模块--可以支持不同的输入时钟 COMPONENT div IS generic (N:integer); PORT ( clk_in : IN STD_LOGIC;--输入 S1 : IN STD_LOGIC;--复位 clk_out : OUT STD_LOGIC--输出时钟 ); END COMPONENT; --秒表控制模块 COMPONENT control PORT ( clk_100Hz : IN STD_LOGIC;--100Hz S2 : IN STD_LOGIC;--启动 S3 : IN STD_LOGIC;--停止 S1 : IN STD_LOGIC;--复位 Millisecond : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--10毫秒BCD码 second : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--秒BCD码 minute : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--分BCD码 hour : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--时BCD码 ); END COMPONENT; --数码管显示模块 COMPONENT display PORT(clk : IN STD_LOGIC; S1 : IN STD_LOGIC; sw_in : IN STD_LOGIC;--量程切换 hour : IN STD_LOGIC_VECTOR(7 DOWNTO 0); Millisecond : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second : IN STD_LOGIC_VECTOR(7 DOWNTO 0); LEDA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); SEL : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; SIGNALhour : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNALMillisecond : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNALminute : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNALsecond : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNALclk_100Hz : STD_LOGIC; SIGNALclk_in : STD_LOGIC; BEGIN --分频到1000Hz--参数化的分频模块--可以支持不同的输入时钟 U1K_div : div generic map(48000) PORT MAP( clk_in => sysclk_in, S1 => S1, clk_out => clk_in ); --分频到100Hz---参数化的分频模块--可以支持不同的输入时钟 U100_div : div generic map(10) PORT MAP( clk_in => clk_in, S1 => S1, clk_out => clk_100Hz ); --秒表计时模块 U_control : control PORT MAP( clk_100Hz => clk_100Hz, S2 => S2, S3 => S3, S1 => S1, hour => hour, Millisecond => Millisecond, minute => minute, second => second ); --显示模块 U_display : display PORT MAP( clk => clk_in, S1 => S1, sw_in=> sw_in,--量程切换 hour => hour, Millisecond => Millisecond, minute => minute, second => second, LEDA => LEDA, SEL => SEL ); END RTL;

完整代码

扫描文章末尾的公众号二维码文章来源地址https://www.toymoban.com/news/detail-771439.html

到了这里,关于Quartus数字秒表verilog代码青创QC-FPGA开发板的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!