注意:后续技术分享,第一时间更新,以及更多更及时的技术资讯和学习技术资料,将在公众号CTO Plus发布,请关注公众号:CTO Plus

FPGA设计Verilog基础之Verilog的运算符Verilog是一种硬件描述语言,支持多种运算符,包括算术运算符、比较(关系)运算符、逻辑运算符、条件运算符https://mp.weixin.qq.com/s?__biz=MzIyMzQ5MTY4OQ==&mid=2247485152&idx=1&sn=28ca47f6cae79f6db708086d6f7c3bad&chksm=e81c25e6df6bacf0cd2d04315c716e870add24c8e1c11be0840a1c7e710bdba157a4a545d427#rd

Verilog是一种硬件描述语言,支持多种运算符,包括算术运算符、比较(关系)运算符、逻辑运算符、条件运算符、位运算符、移位运算符、拼接运算符和其他一些运算符。在进行Verilog开发时,需要熟悉各种运算符的作用和使用方法,以及运算符的优先级。

在前面的文章中已经介绍了一百多个Verilog关键字的特性和使用的总结,详情请参考文末的推荐阅读。

FPGA专栏:https://blog.csdn.net/zhouruifu2015/category_5690253

例如:

module comparator(input a, input b, output eq);

assign eq = (a == b);

endmodule

上述代码定义了一个比较器模块,它有两个输入端口a和b,一个输出端口eq。内部逻辑使用比较运算符实现。

1. 算术运算符

在Verilog HDL语言中,算术运算符又称为二进制运算符。

Verilog支持加、减、乘、除和取模等算术运算符,算术运算符,简单来说,就是数学运算里面的加减乘除,数字逻辑处理有时候也需要进行数字运算,所以需要算术运算符。这些运算符的作用和使用方法如下:

加法运算符(+):将两个数相加。或称为正值运算符。

减法运算符(-):将两个数相减。或称为负值运算符。

乘法运算符(*):将两个数相乘。

除法运算符(/):将两个数相除。

取模运算符(%):求两个数相除的余数。或称为求余运算符。

例如,下面是一个使用算术运算符的示例:

reg [7:0] a, b, c;

assign c = a + b;

assign c = a - b;

assign c = a * b;

assign c = a / b;

assign c = a % b;

Verilog实现乘除比较浪费组合逻辑资源,尤其是除法。一般2的指数次幂的乘除法使用移位运算来完成运算,详情可以看移位运算符部分的内容。非2的指数次幂的乘除法一般是调用现成的IP,QUARTUS/ISE等工具软件会有提供,不过这些工具软件提供的IP也是由最底层的组合逻辑(与或非门等)搭建而成的。

注意: 在进行算术运算操作时,如果某一个操作数有不确定的值x,则整个结果也为不定值x。

2. 比较(关系)运算符

Verilog支持等于、不等于、小于、小于等于、大于和大于等于等比较运算符,关系运算符主要是用来做一些条件判断用的,在进行关系运算符时,如果声明的关系是假的,则返回值是0,如果声明的关系是真的,则返回值是1;所有的关系运算符有着相同的优先级别,关系运算符的优先级别低于算术运算符的优先级别。这些运算符的作用和使用方法如下:

等于运算符(==):判断两个数是否相等。

不等于运算符(!=):判断两个数是否不相等。

小于运算符(<):判断第一个数是否小于第二个数。

小于等于运算符(<=):判断第一个数是否小于等于第二个数。

大于运算符(>):判断第一个数是否大于第二个数。

大于等于运算符(>=):判断第一个数是否大于等于第二个数。

例如,下面是一个使用比较运算符的示例:

reg [7:0] a, b;

wire result;

assign result = (a == b);

assign result = (a != b);

assign result = (a < b);

assign result = (a <= b);

assign result = (a > b);

assign result = (a >= b);

3. 逻辑运算符

Verilog支持与、或、非、异或等逻辑运算符,逻辑运算符是连接多个关系表达式用的,可实现更加复杂的判断,一般不单独使用,都需要配合具体语句来实现完整的逻辑。这些运算符的作用和使用方法如下:

逻辑与运算符(&&):当两个条件都为真时,返回真。

逻辑或运算符(||):当两个条件中至少有一个为真时,返回真。

逻辑非运算符(!):将一个条件取反。

例如,下面是一个使用逻辑运算符的示例:

reg [7:0] a, b;

wire result;

assign result = (a && b);

assign result = (a || b);

assign result = !a;

4. 位(移位)运算符

Verilog支持按位与、按位或、按位异或、按位取反、左移和右移等位运算符,位运算符是一类最基本的运算符,可以认为它们直接对应数字逻辑中的与、或、非门等逻辑门。

位运算符的与、或、非与逻辑运算符逻辑与、逻辑或、逻辑非使用时候容易混淆,逻辑运算符一般用在条件判断上,位运算符一般用在信号赋值上。

移位运算符包括左移位运算符和右移位运算符,这两种移位运算符都用0来填补移出的空位。这些运算符的作用和使用方法如下:

按位与运算符(&):将两个数的二进制位进行与运算。

按位或运算符(|):将两个数的二进制位进行或运算。

按位异或运算符(^):将两个数的二进制位进行异或运算。

按位取反运算符(~):将一个数的二进制位进行取反运算(每个位进行取反)。

左移运算符(<<):将一个数的二进制位向左移动。

右移运算符(>>):将一个数的二进制位向右移动。

例如,下面是一个使用位运算符的示例:

reg [7:0] a, b;

wire result;

assign result = (a & b); // 将 a 的每个位与 b 相同的位进行相与

assign result = (a | b); // 将 a 的每个位与 b 相同的位进行相或

assign result = (a ^ b); // 将 a 的每个位与 b 相同的位进行异或

assign result = ~a; // 将 a 的每个位进行取反

assign result = (a << 2); 将 a 左移 2 位

assign result = (a >> 2); 将 a 右移 2 位

假设a有8bit数据位宽,那么a<<2,表示a左移2bit,a还是8bit数据位宽,a的最高2bit数据被移位丢弃了,最低2bit数据固定补0。如果a是3(二进制:00000011),那么3左移2bit,3<<2,就是12(二进制:00001100)。一般使用左移位运算代替乘法,右移位运算代替除法,但是这种也只能表示2的指数次幂的乘除法。

5. 条件运算符

条件操作符一般来构建从两个输入中选择一个作为输出的条件选择结构(在其他语言中也叫三目运算符),功能等同于always中的if-else语句。

| 符号 |

使用方法 |

说明 |

| ? : |

a ? b : c |

如果 a 为真,就选择 b,否则选择 c |

代码示例:

assign out = (sel == 1) ? in1 : in2;

上述代码中,sel为选择信号,in1和in2为两个输入信号,out为输出信号。当sel等于1时,将in1赋值给out,否则将in2赋值给out。

6. 拼接运算符(Concatation)

Verilog中有一个特殊的运算符是C语言中没有的,就是位拼接运算符。用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。

| 符号 |

使用方法 |

说明 |

| {} |

{a, b} |

将 a 和 b 拼接起来,作为一个新信号 |

代码示例:

wire [7:0] a, b, c;

assign d = {a, b, c};

上述代码中,a、b、c为三个8位输入信号,d为24位输出信号。使用拼接运算符{}将a、b、c拼接成一个24位的信号d。

7. 其他运算符

Verilog还支持其他一些运算符,包括条件运算符(?:)、括号运算符(())、逗号运算符(,)等。这些运算符的作用和使用方法如下:

条件运算符(?:):根据一个条件的真假返回两个不同的值。

括号运算符(()):用于改变运算符的优先级。

逗号运算符(,):用于将多个表达式连接起来。

例如,下面是一个使用其他运算符的示例:

reg [7:0] a, b;

wire result;

assign result = (a > b) ? a : b;

assign result = (a + b) * c;

assign result = (a, b, c);

wire out;

assign out = (a == 1) ? b : c, d;

上述代码中,a为输入信号,b、c、d为三个输出信号,使用逗号运算符将b和c、d连接起来,当a等于1时,将b赋值给out,否则将c和d赋值给out。

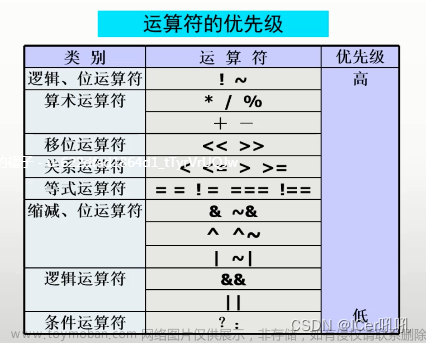

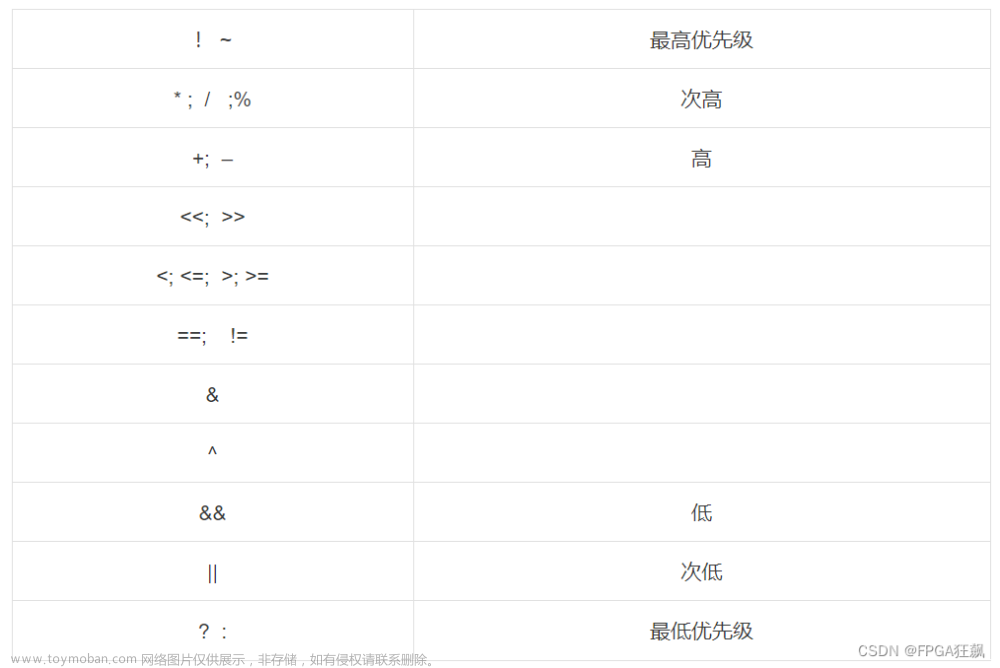

8. 运算符的优先级

在Verilog中,不同运算符的优先级不同,需要注意运算顺序,可以使用括号运算符改变运算符的优先级。

下面是Verilog运算符的优先级,从高到低依次排列:

1. 括号运算符(())

2. 取反运算符(!、~)

3. 乘法运算符(*)、除法运算符(/)、取模运算符(%)

4. 加法运算符(+)、减法运算符(-)

5. 左移运算符(<<)、右移运算符(>>)

6. 比较运算符(<、<=、>、>=、==、!=、===、!==)

6. 按位与运算符(&)

7. 按位异或运算符(^、^~)

8. 按位或运算符(|)

8. 与运算符(&&)

9. 或运算符(||)

10. 条件运算符(?:)

11. 逗号运算符(,)

SteveRocket的博客_CSDN博客-Python进阶,Django进阶,C进阶领域博主SteveRocket擅长Python进阶,Django进阶,C进阶,等方面的知识https://blog.csdn.net/zhouruifu2015/

更多资料 · 微信公众号搜索【CTO Plus】关注后,获取更多,我们一起学习交流。

关于公众号的描述访问如下链接

关于Articulate“做一个知识和技术的搬运工。做一个终身学习的爱好者。做一个有深度和广度的技术圈。”一直以来都想把专业领域的技https://mp.weixin.qq.com/s/0yqGBPbOI6QxHqK17WxU8Q

推荐阅读:

-

FPGA在工业缺陷检测上的应用实践

-

FPGA设计Verilog基础之Verilog全局变量和局部变量定义

-

FPGA设计Verilog基础之Verilog中clk为什么要用posedge,而不用negedge

-

初学者必须弄懂的一些基本FPGA设计概念(1)

-

工作总结之全网最全的103个Verilog关键字总结(上)

-

工作总结之全网最全的103个Verilog关键字总结(下)

-

5G时代的FPGA发展趋势和应用分析

-

FPGA结合chatgpt的应用开发实践

-

FPGA | FPGA设计流程指南 v2.0

-

设计规范 | 总结开发过程中DDR3和FPGA部分的设计规范

-

术语一览 | 总结开发过程中关于FPGA的专业术语文章来源:https://www.toymoban.com/news/detail-771460.html

-

用AI帮我写一篇关于FPGA的文章,并推荐最热门的FPGA开源项目文章来源地址https://www.toymoban.com/news/detail-771460.html

到了这里,关于FPGA设计Verilog基础之Verilog的运算符的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!